### **TESIS DOCTORAL**

# Convertidor Electrónico Reductor/Elevador para la Conexión Activa De Instalaciones Fotovoltaicas a la Red

### **CARLOS RONCERO CLEMENTE**

### DEPARTAMENTO DE INGENIERÍA ELÉCTRICA, ELECTRÓNICA Y AUTOMÁTICA

Conformidad de los Directores

Fdo: Enrique Romero Cadaval Fdo: Eva González Romera

### **DOCTORAL THESIS**

# **Buck/Boost Electronic Converter for Active Con- nection of Photovoltaic Installations to the Grid**

### **CARLOS RONCERO CLEMENTE**

Power Electrical and Electronic System Research Group (PE&ES)

DEPARTMENT OF ELECTRICAL, ELECTRONIC AND CONTROL

ENGINEERING

Approval by supervisor and co-supervisor

Fdo: Enrique Romero Cadaval Fdo: Eva González Romera

### **Declaration**

I hereby declare that this submission is my own work and achievement for the doctoral degree at University of Extremadura, and it does not contain material which has been accepted for the award of any other academic degree or diploma of the university or other institute of higher learning.

Carlos Roncero Clemente

## Acknowledgements

The work that this PhD Thesis has involved would have not been possible without the collaboration and support of many different people. I would like to dedicate to them the next words.

First and foremost, I would like to thank Prof. Enrique Romero Cadaval for his excellent supervision, constant support and valuable guidance during all my stage as PhD student. Enrique has been willing to help and to teach me, in order to solve any problem with his innovative ideas and creativity. His confidence in me anytime was really important and I confirm that he is my mentor as researcher. At the same time, I want to thank to my co-supervisor Prof. Eva González Romera her work. She has helped me any time I needed as well as the good job she has done to improve the quality of this document, always with good manners.

The majority of my research work has been carried out with the research group *Power Electrical and Electronic System from University of Extremadura*. I want to express my maximum appreciation to each member: Prof. Fermín Barrero González, Prof. María Isabel Milanés Montero, Dr. Víctor Miñambres, Pedro González, Miguel Ángel Guerrero and Javier Gallardo for insightful and continuous technical advices in the laboratory.

I also would like to express my sincere gratitude to Dr. Dmitri Vinnikov for giving me the opportunity of developing an important part of this work at the Department of Electrical Engineering of Tallinn University of Technology during two periods. I want to stand out among his team to Dr. Oleksandr Husev. He has been a key researcher of this PhD Thesis who I have spent much time working with. I would like to thank to him his interest, encouragement and enthusiasm during our collaborations.

I am very grateful as well to Prof. Josep Maria Guerrero for hosting my stage in a top research centre in Europe as the Department of Energy Technology in Aalborg University, providing lab facilities and for his warm hospitality.

I would like to acknowledge the financial support from *Ministerio de Economía and Competitividad (Gobierno de España)* and to *Gobierno de Extremadura*, which made this research possible through different projects and grants.

I am really grateful to all my friends, especially to Ángel and Vicente. They have been there always when it matters.

Finally, I have no words to express my gratefulness to my relatives and especially to my parents and to my wife Julita for their boundless love. They make sense of all of this work.

### **Abstract**

Shortage of fossil fuel and the necessity of reducing  $CO_2$  emissions among other reasons have significantly grown the number of the inverter-based distributed generator connected to the low-voltage distribution network. Many of them interact with renewable energy sources such as photovoltaic modules and wind turbines, besides they are present in any energy storage process.

Focusing the attention on the photovoltaic systems, it has been observed that for a long time, photovoltaic inverter function was merely to inject power into the main grid with a unitary power factor but, new trends and policies propose to integrate them as active and smart devices. This current philosophy contributes to the change from the traditional and linear power systems to the smartgrid and microgrid concepts. In this way, inverters would be able to contribute to the local voltage support, improve the power quality and give rise to flexibility and security of supply.

Concurrently industry and research are aiming at cost reductions and enhanced performance of the energy conversion process, with a focus on the inverter topologies. Photovoltaic inverters are traditionally characterized by two-stage conversion process, composed by a dc-dc boost converter and the voltage source inverter. Some innovative ideas seem quite suitable for this application because they can step up the dc input voltage in a single power conversion stage by using impedance source network, quasi impedance network or its derivations. This family of converters allows among other advantages the following: voltage boost/buck, extended range of operation, low cost and high efficiency, strong electromagnetic immunity, no need for dead time, minimum number of semiconductor devices, improved reliability and performance, and short-circuit protection. Furthermore, impedance networks have been integrated with multilevel bridges to acquire their intrinsic advantages.

However, because of the relatively early stage, only few studies deal with the grid-connected integration with closed loop control systems, which basically must provide coexistence of an operation strategy of the inverter, a maximum power point tracker algorithm, a dc-link voltage control method and a special modulation technique to embed the shoot-through states into the normal ones.

This PhD research presents a novel solution for energy conversion in photovoltaic applications based on the aforementioned concepts. A new inverter topology called "three-level neutral-point-clamped quasi-impedance source inverter" both in single and

in three phase variants is proposed, analysed and calculated along a new modulation technique to generate the shoot-through states uniformly distributed during the whole fundamental period. To operate in grid-connected mode and deal with the aforementioned new trends related to the electrical systems, different closed loop operation strategies are designed and proposed as well. Taking into account these last functionalities, the proposed inverter is considered as an active device, presenting a smart behaviour in its integration with the main grid.

### Resumen

La escasez de las fuentes de energía basadas en combustibles fósiles y la necesidad de reducir las emisiones de CO<sub>2</sub>, entre otros motivos, han provocado un aumento en la conexión a las redes de distribución de baja tensión de generadores distribuidos que emplean inversores. Muchos de ellos actúan de interfaz con fuentes de energías renovables como módulos fotovoltaicos y turbinas eólicas, además de formar parte de cualquier sistema de almacenamiento de energía.

Particularizando en los sistemas de generación fotovoltaica, se observa que durante mucho tiempo y desde sus inicios, estos inversores han estado actuando básicamente mediante la inyección de potencia activa en la red, con factor de potencia unitario. Pero las nuevas tendencias de operación e incluso normativas de distintos países, proponen que estos dispositivos sean integrados como elementos más activos e inteligentes. Esta filosofía en la operación contribuye a la evolución de los tradicionales sistemas de potencia lineales hacia los conocidos conceptos de microrredes y redes inteligentes. De esta manera, los inversores contribuirían al control de tensión en el nodo a nivel local y mejorarían la calidad de la energía, además de contribuir a una mayor flexibilidad y seguridad del suministro eléctrico.

Simultáneamente a esta tendencia de operación, la industria y los grupos de investigación se han planteado como reto el reducir el coste y mejorar los rendimientos de los procesos de conversión de energía, focalizando la atención en las topologías inversoras. Los inversores fotovoltaicos tradicionales se caracterizan por contar con una doble etapa de conversión de energía, a través de un convertidor continua-continua elevador y un inversor en fuente de tensión. Algunas de las ideas innovadoras en este campo parecen muy adecuadas para aplicaciones fotovoltaicas dado que pueden elevar la tensión continua de entrada en una sola etapa de conversión a través del uso de una red impedante o alguna de sus derivadas. Esta familia de convertidores permite: elevar y reducir la tensión, dotar al convertidor de un mayor rango de operación en cuanto a tensión de entrada, menor coste y mayor eficiencia, mayor inmunidad electromagnética, ausencia de necesidad de tiempos muertos, mayor rendimiento y protección frente a cortocircuitos de rama, entre otros.

Sin embargo, dada la reciente aparición de estos convertidores, no existen demasiados estudios en cuanto a su integración como elementos conectados a la red con algoritmos de control en lazo cerrado, en los cuales deben coexistir una estrategia de operación del inversor, un algoritmo del punto de máxima potencia, un método de control del bus de

continua y una técnica de modulación especial que permita generar estados de conducción simultáneo entre interruptores de la misma rama además de los estados normales.

Esta tesis doctoral presenta una solución novedosa para la conversión de energía en sistemas fotovoltaicos teniendo en cuenta los aspectos previos. Se propone, analiza y calcula una nueva topología inversora conocida como "inversor de tres niveles con el punto neutro fijado con fuente cuasi impedante", tanto en versión monofásica como en trifásica. También se propone una nueva técnica de modulación que permite generar los estados de conducción simultánea entre interruptores de una misma rama de manera uniforme durante todo el periodo fundamental. Por último, se han desarrollado y propuesto diferentes algoritmos de control en lazo cerrado para su operación en conexión a red. Teniendo en cuenta estas últimas funcionalidades añadidas, el convertidor propuesto se considera un elemento activo, comportándose de manera inteligente en lo que respecta a su conexión y operación con la red principal.

# **Table of Contents**

| Declaration                                  | iv       |

|----------------------------------------------|----------|

| Acknowledgements                             | v        |

| Abstract                                     | vii      |

| Resumen                                      | ix       |

| Table of Contents                            | xi       |

| List of Figures                              | xv       |

| List of Tables                               | xxi      |

| Nomenclature                                 | 1        |

| 1 Introduction                               | 7        |

| 1.1 Photovoltaic energy injection into the g | grid7    |

| 1.2 Thesis motivation                        | 9        |

| 1.3 Objectives of the thesis                 | 10       |

| 1.4 Structure of the thesis                  | 11       |

| 1.5 Results, novelties and dissemination     | 12       |

| 2 Three-Level Neutral-Point-Clamped qZSI     | Topology |

| 2.1 Introduction                             | 15       |

| 2.2 Two-level traditional VSI topologies     | 16       |

| 2.2.1 Single phase                           | 16       |

| 2.2.2 Three phase                            | 20       |

| 2.3 Two-level ZS dc/ac converter topologic   | es21     |

| 2.4 Multilevel dc/ac converter topologies    | 25       |

| 2.5 ZS multilevel dc/ac converter topologie  | es 30    |

|   | 2.5.1           | State of the art                                                                                         | 30   |

|---|-----------------|----------------------------------------------------------------------------------------------------------|------|

|   | 2.5.2           | Proposed three-level neutral-point-clamped qZS dc/ac converter topology                                  | 36   |

| 3 |                 | r                                                                                                        | 51   |

|   | 3.1 Intr        | oduction                                                                                                 | 51   |

|   | 3.2 Two         | o-level modulation techniques                                                                            | 51   |

|   | 3.3 Mu          | Itilevel modulation techniques                                                                           | 55   |

|   | 3.4 Exi         | sting modulation techniques oriented to two-level ZS dc/ac converters .                                  | 56   |

|   | 3.4.1           | Simple boost control                                                                                     | 57   |

|   | 3.4.2           | Maximum boost control                                                                                    | 58   |

|   | 3.4.3           | Maximum constant boost control                                                                           | 59   |

|   | 3.4.4           | Analytical comparison                                                                                    | 62   |

|   | 3.5 Mo          | dulation techniques for ZS multilevel dc/ac converters                                                   | 64   |

|   | 3.5.1           | State of the art                                                                                         | 64   |

|   | 3.5.2           | Proposed modulation techniques for three-level neutral-point-clamped qZS inverter                        | 71   |

|   | 3.5.3           | Experimental results                                                                                     | 77   |

| 4 |                 | ion Strategies for Performing Grid-Connected Inverter Active                                             | 85   |

|   | 4.1 Intr        | oduction                                                                                                 | 85   |

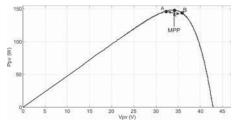

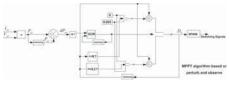

|   |                 | ximum power point tracking algorithm for three-level neutral-point-<br>nped qZS inverter                 | 86   |

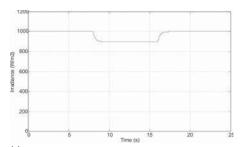

|   | 4.2.1           | Simulation study                                                                                         | 89   |

|   | 4.2.2           | Experimental results                                                                                     | 91   |

|   | 4.3 <i>P</i> at | nd Q regulation                                                                                          | 92   |

|   | 4.3.1           | P and Q operation strategies for traditional inverter topologies                                         | 92   |

|   | 4.3.2           | Proposed operation strategies for P and Q regulation in a three-level neutral-point-clamped qZS inverter | 98   |

|   | 4.3.3           | Integration with energy storage systems                                                                  | .111 |

|   | 4.4 Act         | ive filtering functions                                                                                  | .116 |

| 5 | Conclu          | sions and Future Works                                                                                   | 121  |

| 5.1     | Summary of key results            | 121 |

|---------|-----------------------------------|-----|

| 5.2     | Future work                       | 122 |

| 5.3     | Resumen de resultados principales | 122 |

| 5.4     | Trabajos futuros                  | 124 |

| Bibliog | graphy                            | 125 |

| Appen   | dix                               | 139 |

| Short ( | Curriculum Vitae                  | 257 |

# **List of Figures**

| Fig. 1.1. a) 2013 fuel shares in world total primary energy supply. b) 2013                                            |    |

|------------------------------------------------------------------------------------------------------------------------|----|

| product shares in world renewable energy supply.                                                                       | 7  |

| Fig. 1.2. Annual growth rates of world renewable supply from 1990 to 2013                                              | 8  |

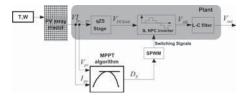

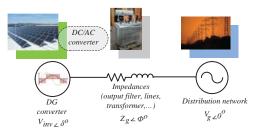

| Fig. 1.3. General scheme of a grid-connected photovoltaic system                                                       |    |

| Fig. 2.1. Principle of operation of an inverter.                                                                       |    |

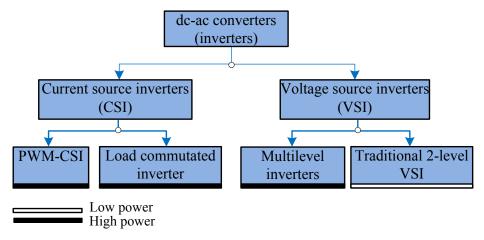

| Fig. 2.2. Inverter topology traditional classification.                                                                | 16 |

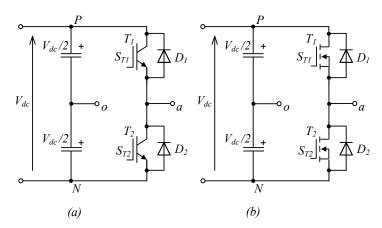

| Fig. 2.3. a) Half-bridge inverter topology with IGBT. b) With MOSFET                                                   | 17 |

| Fig. 2.4. Half-bridge inverter conduction states when a) $v_{ao} = V_{dc}/2$ and $i_a < 0$ ,                           |    |

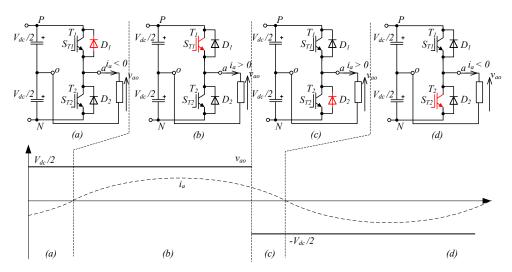

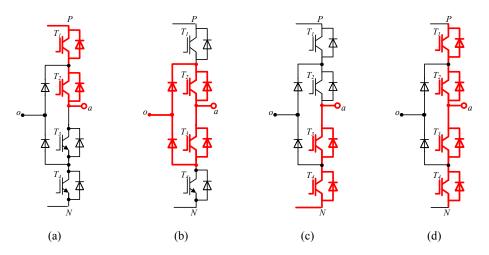

| b) $v_{ao} = V_{dc}/2$ and $i_a > 0$ , c) $v_{ao} = -V_{dc}/2$ and $i_a > 0$ and d) $v_{ao} = -V_{dc}/2$ and $i_a < 0$ | 18 |

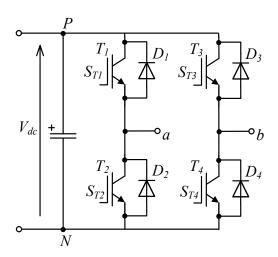

| Fig. 2.5. H-bridge inverter power circuit (IGBT based).                                                                |    |

| Fig. 2.6. H-bridge switching states. a) $v_{ab} = V_{dc}$ , b) $v_{ab} = 0$ , c) $v_{ab} = -V_{dc}$ and d)             |    |

| $v_{ab} = 0$                                                                                                           | 19 |

| Fig. 2.7. Full-bridge three-phase VSI topology (with Y-connected load)                                                 | 20 |

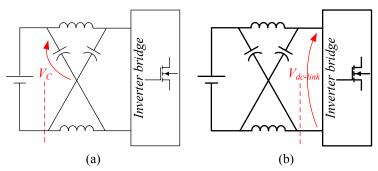

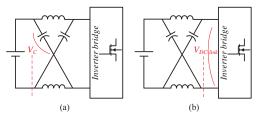

| Fig. 2.8. General representation of a) ZSI and b) qZSI                                                                 | 22 |

| Fig. 2.9. Equivalent circuits during nonshoot-through state a) ZSI, c) qZSI; and                                       |    |

| during shoot-through state b) ZSI and d) qZSI.                                                                         | 23 |

| Fig. 2.10. Some derived qZS inverters. a) First extension of the capacitor-                                            |    |

| assisted EB-qZSN, b) Second extension of the capacitor-assisted EB-qZSN, c)                                            |    |

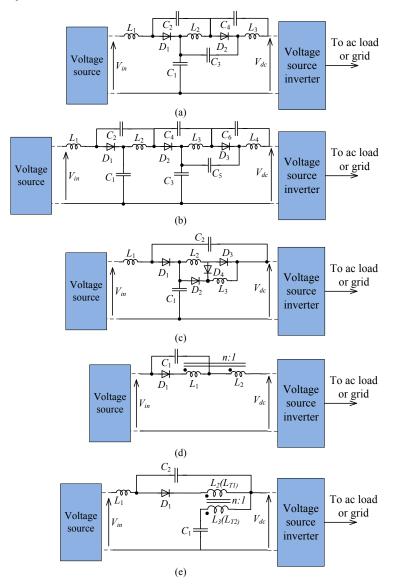

| SL-qZSN, d) trans-qZSN ( $n\geq 1$ ), e) LCCT-qZSN ( $n\geq 1$ )                                                       | 24 |

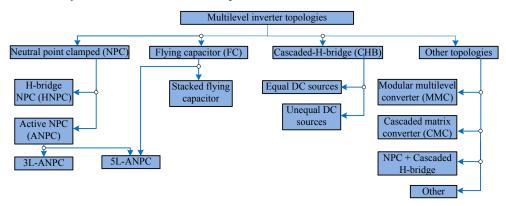

| Fig. 2.11. Multilevel inverter classification.                                                                         | 25 |

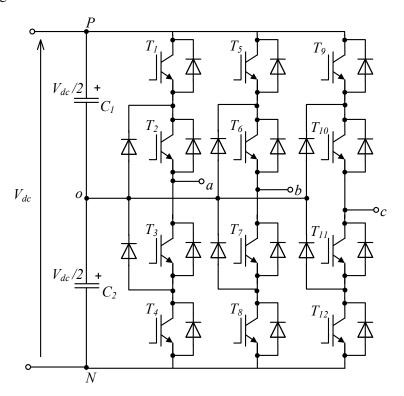

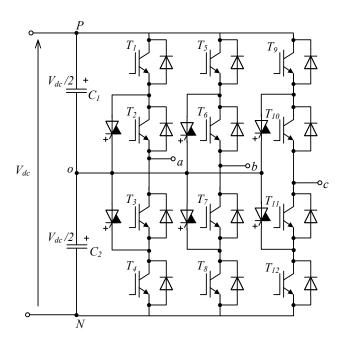

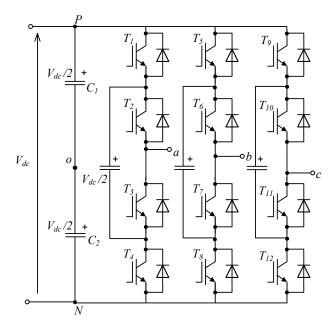

| Fig. 2.12. Three-phase three-level NPC inverter.                                                                       | 26 |

| Fig. 2.13. Three-phase three-level ANPC inverter                                                                       | 27 |

| Fig. 2.14. Three-phase three-level FC inverter.                                                                        | 27 |

| Fig. 2.15. Two-cell FC topology.                                                                                       | 28 |

| Fig. 2.16. Two-cell CHB inverter.                                                                                      | 28 |

| Fig. 2.17. MMC inverter.                                                                                               | 29 |

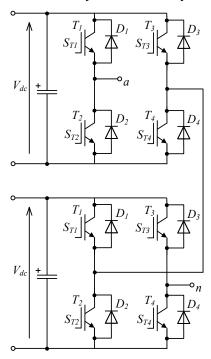

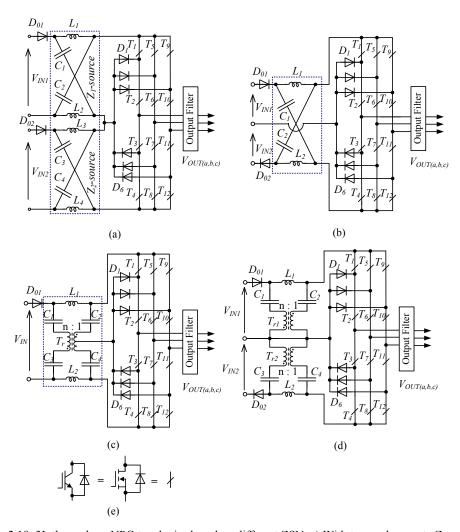

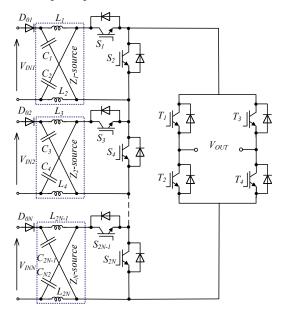

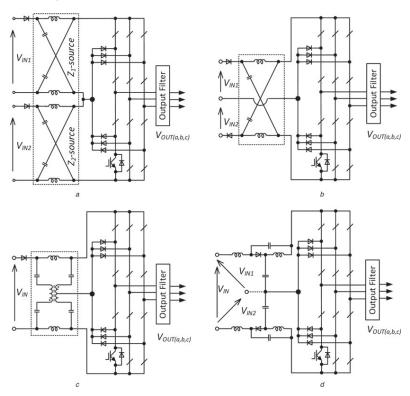

| Fig. 2.18. 3L three-phase NPC topologies based on different ZSN. a) With two                                           |    |

| and separate Z-source network and input voltage sources, b) With single ZSN                                            |    |

| and separate input voltage source, c) Transformer Z-source NPC with single                                             |    |

| input voltage source, d) Transformer Z-source NPC inverter with separate                                               |    |

| input voltage sources, e) Generalization of power switch                                                               | 31 |

| Fig. 2.19. a) Four-level Z-source inverter of Diode Clamped type. b) Five-level                                        |    |

| Z-source inverter of Diode Clamped type                                                                                | 32 |

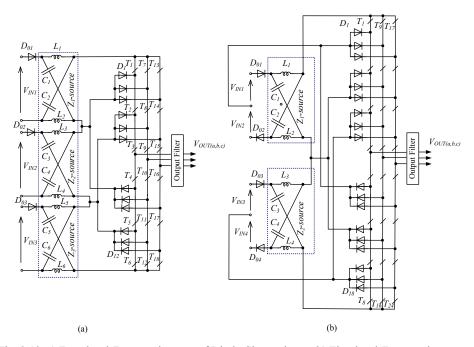

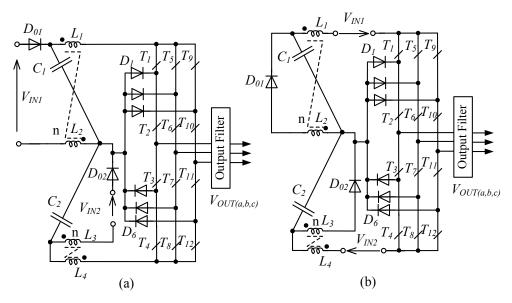

| Fig. 2.20. Modifications of the 3L Z-source based inverters: a) 3L DCLC                                                                                  |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| inverter with two Z-source networks, b) 3L dual inverter with two Z-source                                                                               |            |

| networks, c) 3L dual inverter with single Z-source network                                                                                               | 33         |

| Fig. 2.21 Seven-level Z-source based inverter.                                                                                                           | 33         |

| Fig. 2.22. Z-source-based MLI with reduction of switches                                                                                                 | 34         |

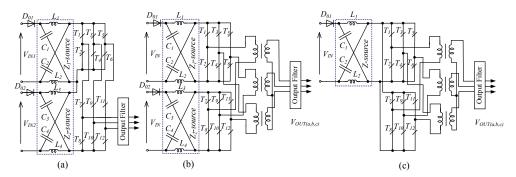

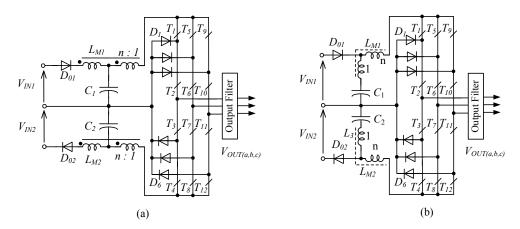

| Fig. 2.23. a) 3L NPC trans-Z-source inverter and b) 3L NPC trans-quasi-Z-                                                                                |            |

| source inverter.                                                                                                                                         | 35         |

| Fig. 2.24 a) Other 3L NPC trans-Z-source inverter and b) 3L NPC - Γ source                                                                               |            |

| inverter.                                                                                                                                                | 36         |

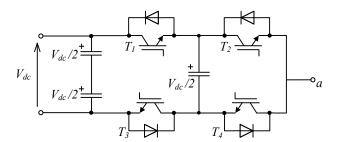

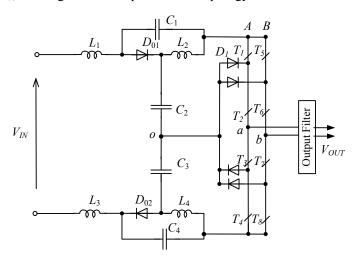

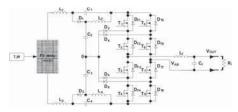

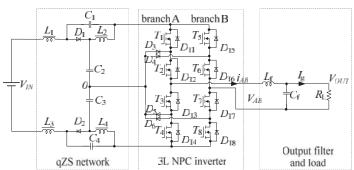

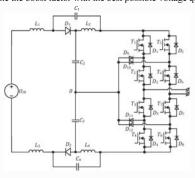

| Fig. 2.25. New proposed quasi-Z source NPC inverter: single phase case study                                                                             |            |

| system                                                                                                                                                   | 37         |

| Fig. 2.26. Different switching states per branch in the qZS NPC inverter. a) $u_{ao}$                                                                    |            |

| $= B (V_{dc}/2)$ . b) $u_{ao} = 0$ . c) $u_{ao} = -B (V_{dc}/2)$ . d) ST state                                                                           | 38         |

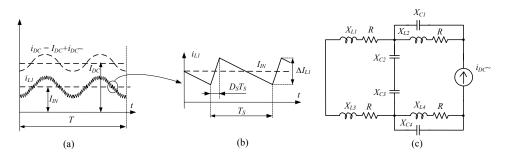

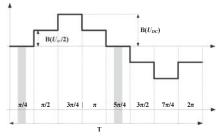

| Fig. 2.27. a) Idealised operating waveforms at low frequency view. b) At high                                                                            |            |

| frequency. c) Equivalent circuit.                                                                                                                        | 40         |

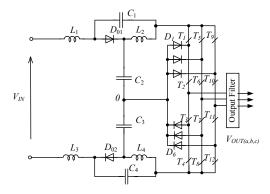

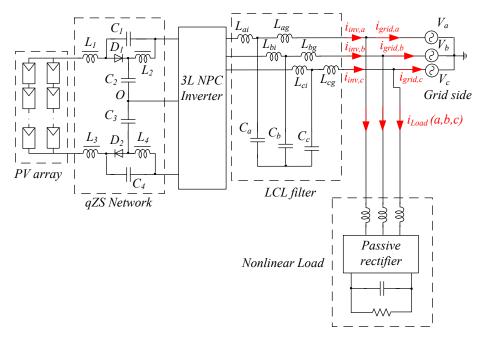

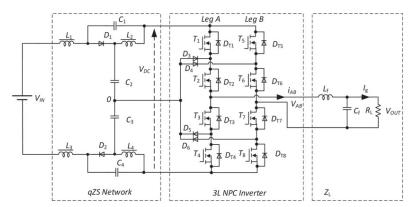

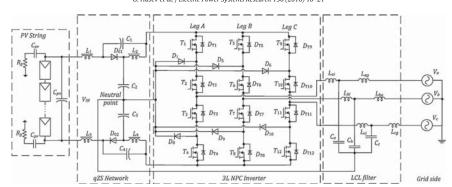

| Fig. 2.28. New proposed quasi-Z source NPC inverter: Three phase case study                                                                              |            |

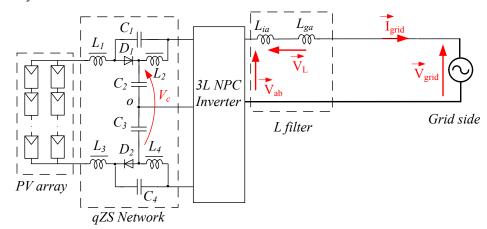

| system.                                                                                                                                                  | 41         |

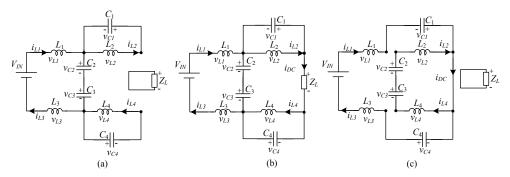

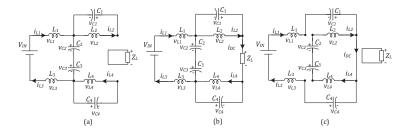

| Fig. 2.29. Equivalent circuits. a) Zero states. b) Active states. c) ST states                                                                           | 42         |

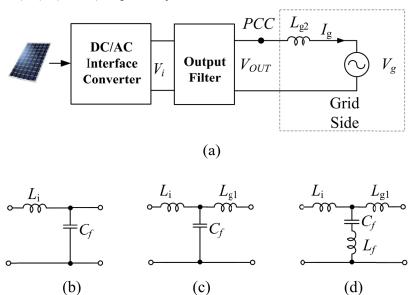

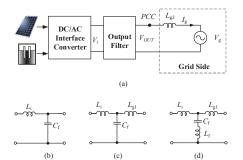

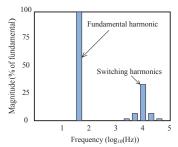

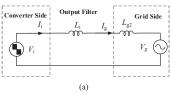

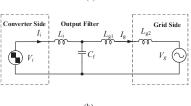

| Fig. 2.30. a) General scheme of a grid-connected PV system. b) LC-filter. c)                                                                             |            |

| LCL-filter and d) LLCL-filter.                                                                                                                           | 43         |

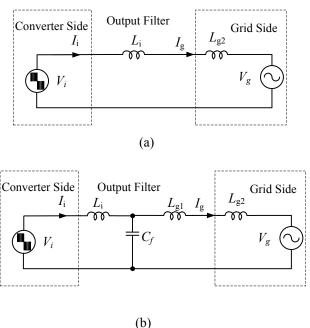

| Fig. 2.31. Equivalent circuit of a) <i>L</i> -filter and b) <i>LCL</i> -filter                                                                           | 44         |

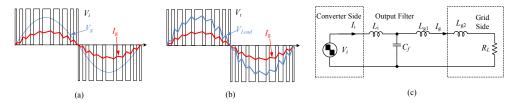

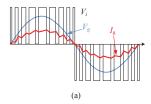

| Fig. 2.32. a) Voltage and current waveforms of the grid-connected, b)                                                                                    |            |

| islanding mode system and c) equivalent grid-connected converter with output                                                                             |            |

| filter at rated power.                                                                                                                                   | 46         |

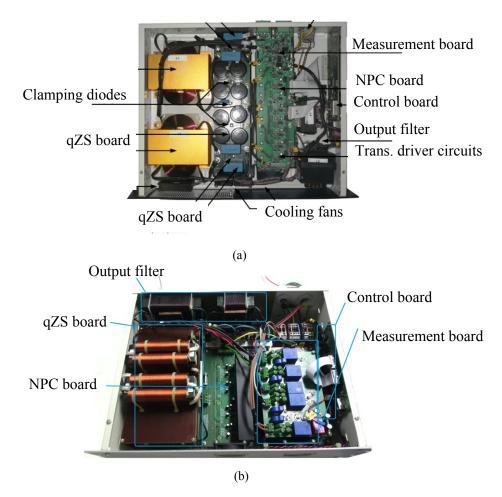

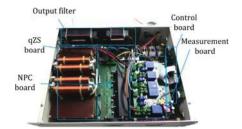

| Fig. 2.33. Pictures of the final prototypes of 3L-NPC-qZSI. a) Single-phase                                                                              |            |

| system. b) Three-phase system.                                                                                                                           | 49         |

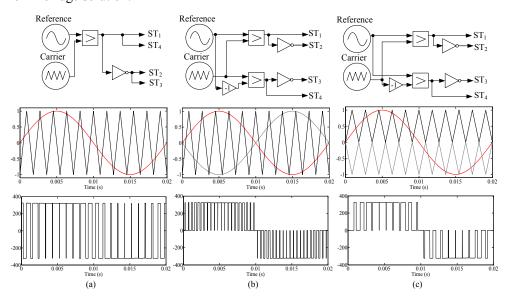

| Fig. 3.1. Sinusoidal PWM for H-bridge topology: a) Bipolar PWM, b)                                                                                       |            |

| Unipolar PWM, c) Hybrid PWM.                                                                                                                             | 52         |

| Fig. 3.2. Control signals involved in the modulation for two-level three-phase                                                                           |            |

| inverter.                                                                                                                                                | 53         |

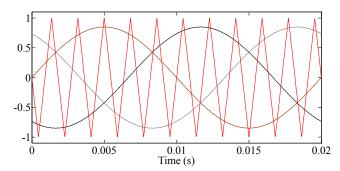

| Fig. 3.3. Modulation waveforms of different PWM methods with zero                                                                                        |            |

| sequence voltage addition ( $u_{cmv}$ ). a) THIPWM, b) SVPWM, c) DPWMMAX                                                                                 | <i>5</i> 4 |

| and d) DPWMMIN                                                                                                                                           | 54         |

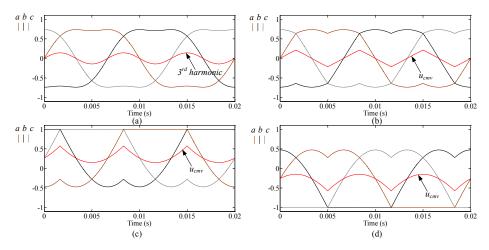

| Fig. 3.4. Modulation waveforms of different PWM methods. Continuation. a)                                                                                | <i>-</i> 1 |

| DPWM0, b) DPWM1, c) DPWM2 and d) DPWM3                                                                                                                   | 54         |

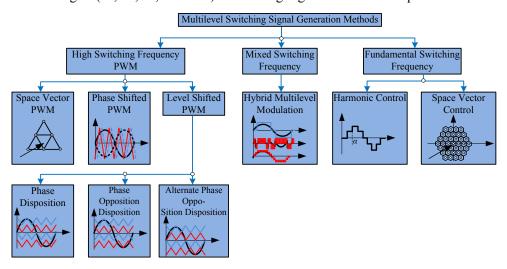

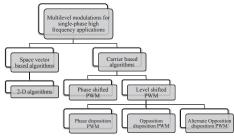

| Fig. 3.5. Classification of multilevel modulation methods according to                                                                                   |            |

| switching frequency.                                                                                                                                     | 55         |

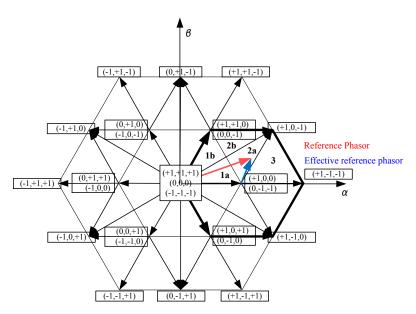

| Fig. 3.6. Vectorial representation of states in a NPC inverter.                                                                                          | 56         |

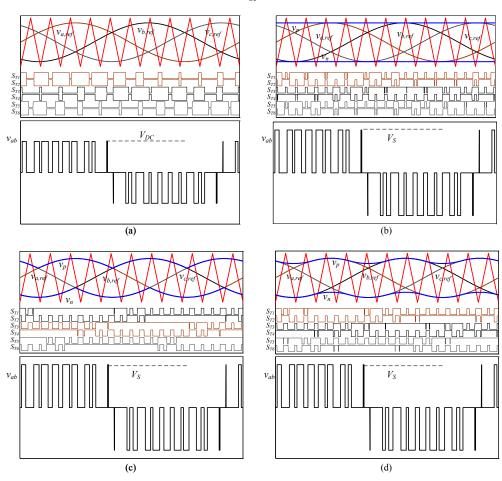

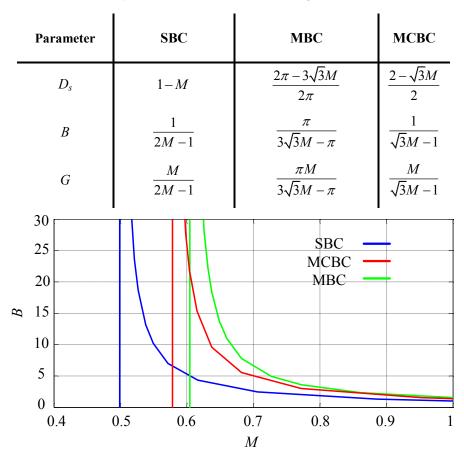

| Fig. 3.7. a) Traditional carrier-based PWM. b) Simple boost control method. c)                                                                           | 60         |

| Maximum boost control method. d) Maximum constant boost control method<br>Fig. 3.8. Relationship between <i>B</i> and <i>M</i> in each modulation method | 61         |

| 11g. J.o. Kelanonship utiweth D and M in each inoquiation inclied                                                                                        | บ1         |

| Fig. 3.9. Simulation waveforms of: a) VSC with traditional sinusoidal PWM,                              |       |

|---------------------------------------------------------------------------------------------------------|-------|

| b) ZSI with simple boost control, c) ZSI with maximum boost control, d) ZSI                             |       |

|                                                                                                         | . 63  |

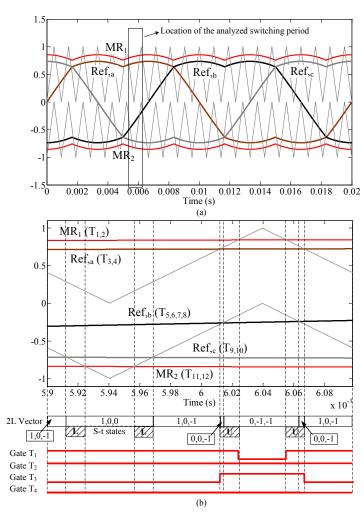

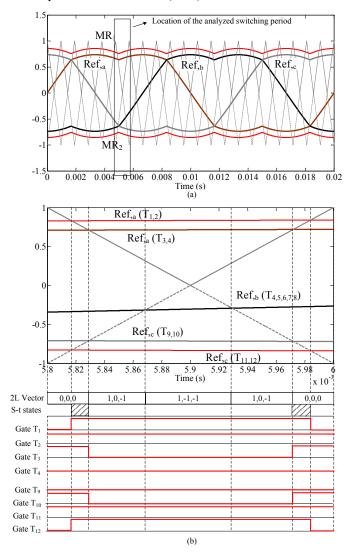

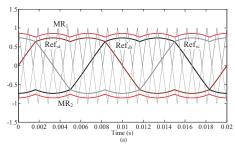

| Fig. 3.10. NTV/MR PWM scheme. a) Reference and carrier arrangement. b)                                  |       |

| Vectorial analysis of a switching period.                                                               | . 65  |

| Fig. 3.11. RCM PWM scheme. a) Reference and carrier arrangement for two-                                |       |

| level (2L) formulation. b) Vectorial analysis for 2L formulation in a switching                         |       |

| period. c) Logic mapping from 2L to RCM 3L                                                              | . 66  |

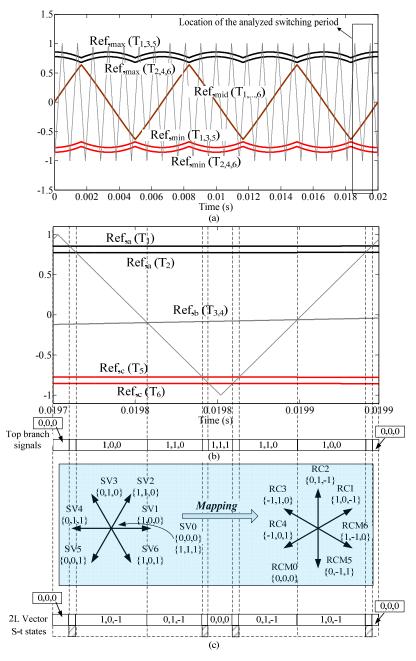

| Fig. 3.12. EI scheme. a) Reference and carrier arrangement. b) Vectorial                                |       |

| analysis of a switching period.                                                                         | 67    |

| Fig. 3.13. APOD scheme. a) Reference and carrier arrangement. b) Vectorial                              |       |

| analysis of a switching period.                                                                         | 69    |

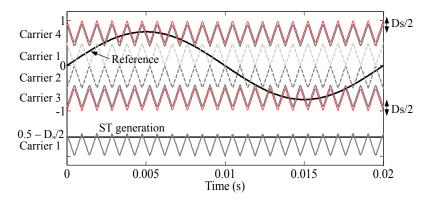

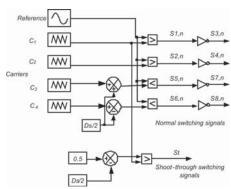

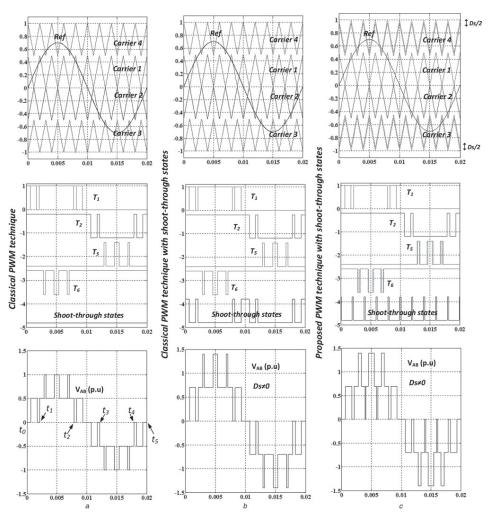

| Fig. 3.14. Sketch of the proposed modulation technique with uniformly                                   | . 0 ) |

| distributed shoot-through states and constant width.                                                    | 71    |

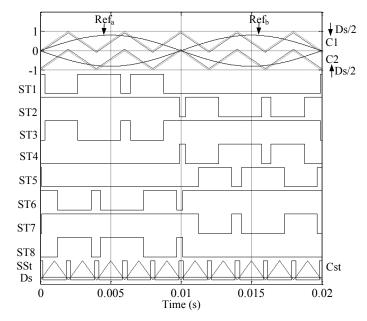

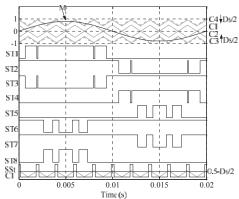

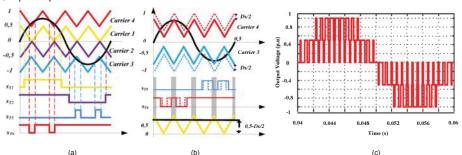

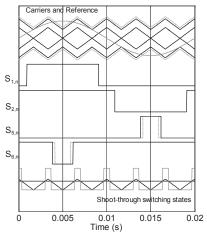

| Fig. 3.15. Switching pattern of the first proposed modulation technique.                                |       |

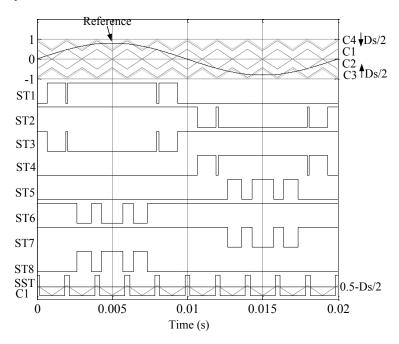

| Fig. 3.16. Sketch of the proposed modulation technique with balanced power losses.                      |       |

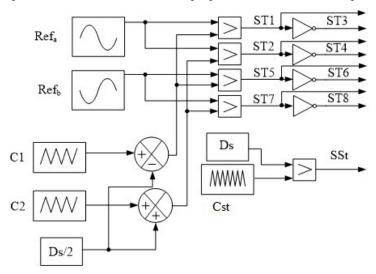

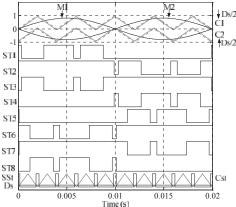

| Fig. 3.17. Switching signals generation of the second proposed modulation                               | , 5   |

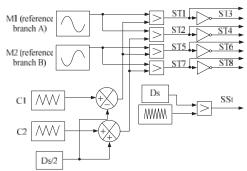

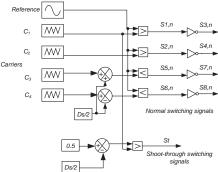

| technique                                                                                               | 73    |

| Fig. 3.18. Sketch of the implementation of the second modulation technique.                             |       |

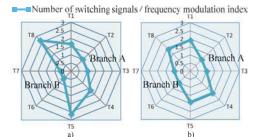

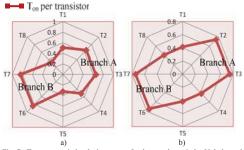

| Fig. 3.19. Number of switching signals per switch/ $m_f$ in one fundamental                             | , , , |

| period. a) First modulation technique. b) Second proposed modulation                                    |       |

| technique. Ton per switch during one fundamental period. c) First modulation                            |       |

| technique. (d) Second proposed modulation technique                                                     | 75    |

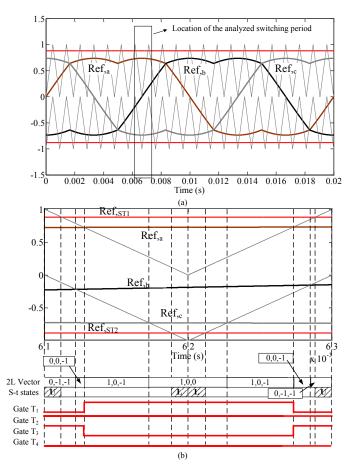

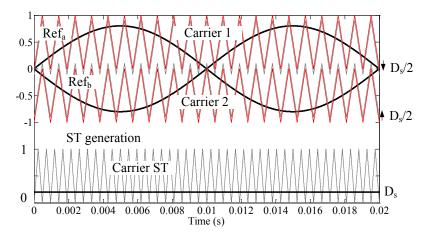

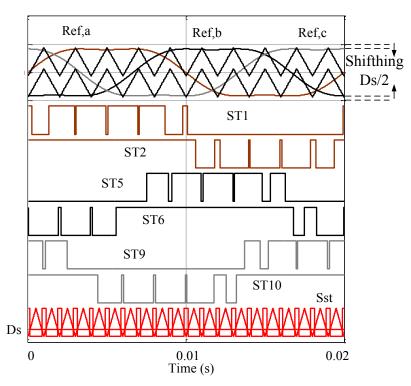

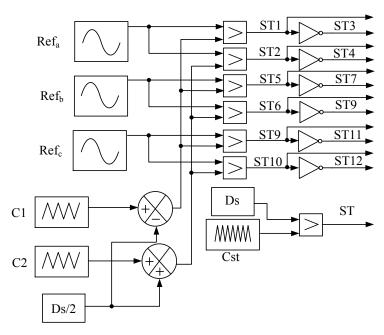

| Fig. 3.20. Sketch of the proposed three-phase PWM technique.                                            |       |

| Fig. 3.21. Implementation sketch of the proposed three-phase PWM technique                              |       |

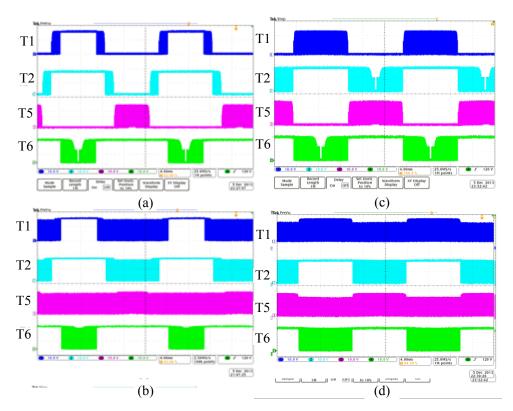

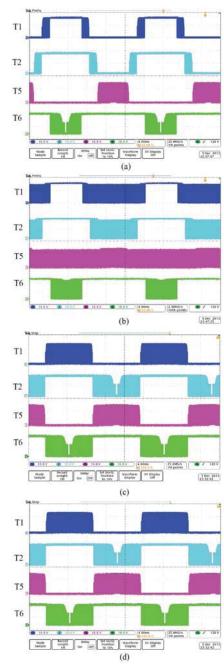

| Fig. 3.22. Gate-source switching signals of the first (a, b) and second (c, d)                          | , , , |

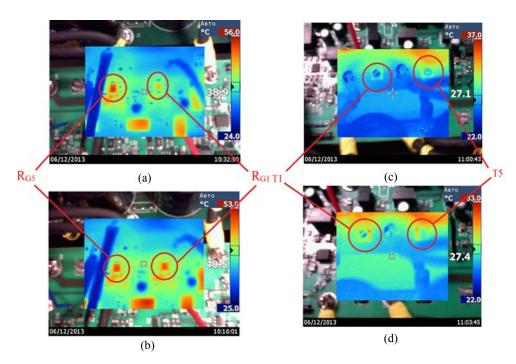

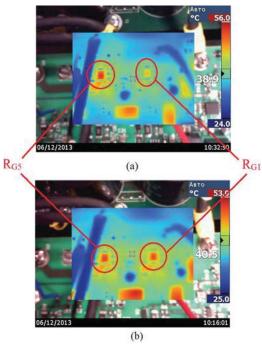

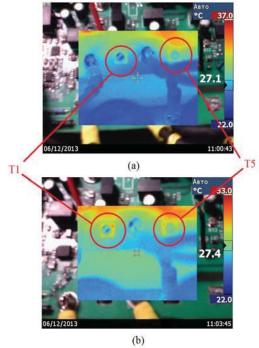

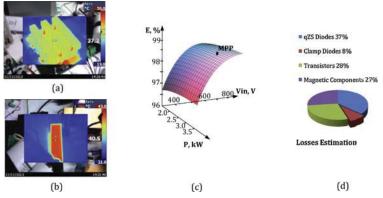

| modulation techniques without (a, c) and with (b, d) ST states                                          | 78    |

| Fig. 3.23. Thermal pictures of the gate resistors of the transistors T1 and T5                          | , 70  |

| under a) first modulation and b) second modulation technique. Thermal                                   |       |

| pictures of the transistor chips T1 and T5 under c) first and d) second                                 |       |

|                                                                                                         | . 79  |

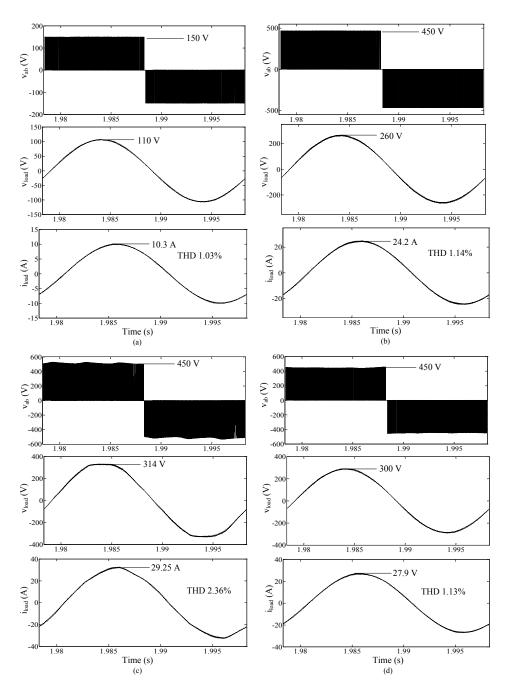

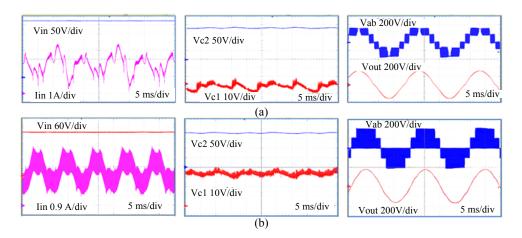

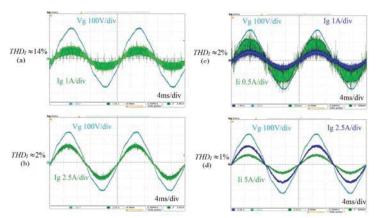

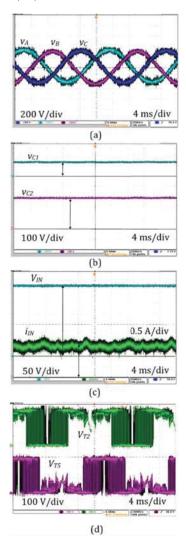

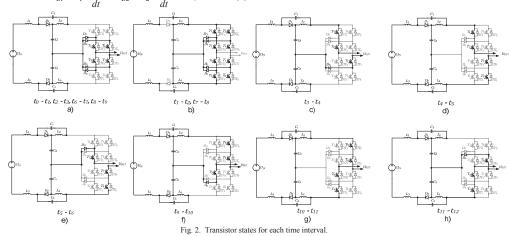

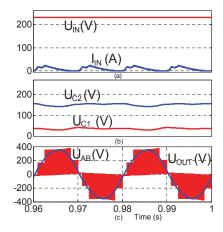

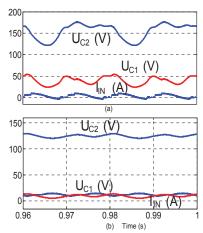

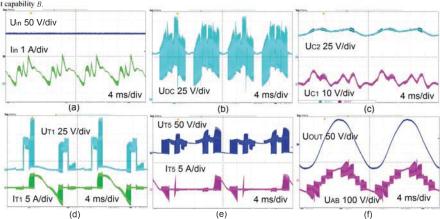

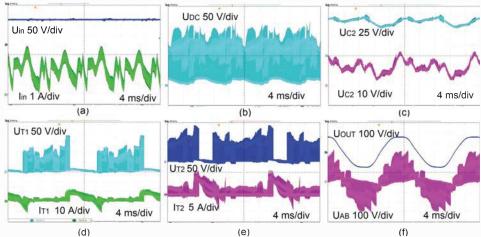

| Fig. 3.24. Experimental results of the single-phase 3L-NPC-qZSI. a) Without                             | . 19  |

|                                                                                                         | . 80  |

| ST. b) With ST.                                                                                         | . 00  |

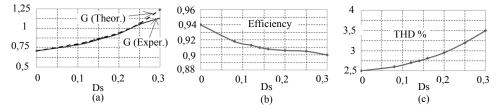

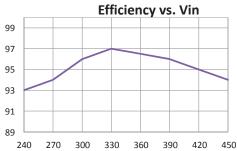

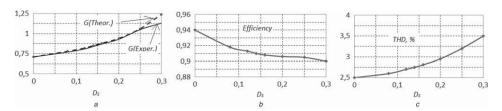

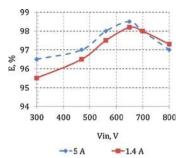

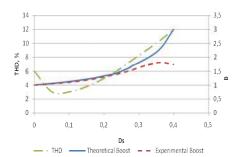

| Fig. 3.25. Experimental measurements of the single-phase converter. a)                                  |       |

| Comparison of the gain factors obtained analytically (dashed line) and                                  |       |

| experimentally (solid line) versus D <sub>s</sub> , b) Dependence of efficiency with the D <sub>s</sub> | 00    |

| , ,                                                                                                     | . 80  |

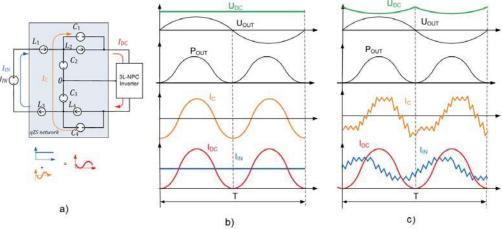

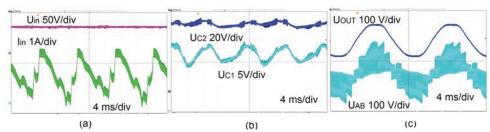

|                                                                                                         | . 81  |

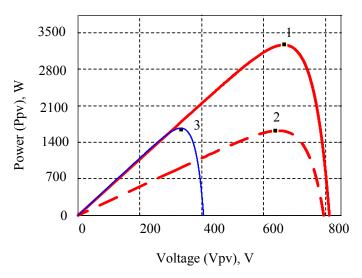

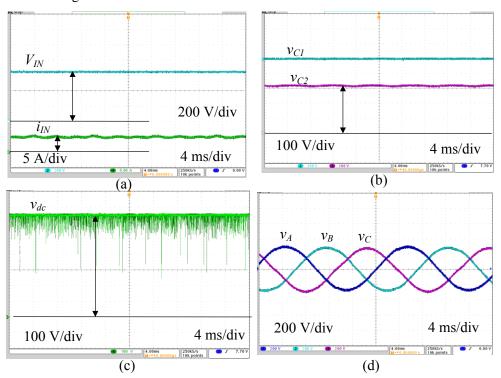

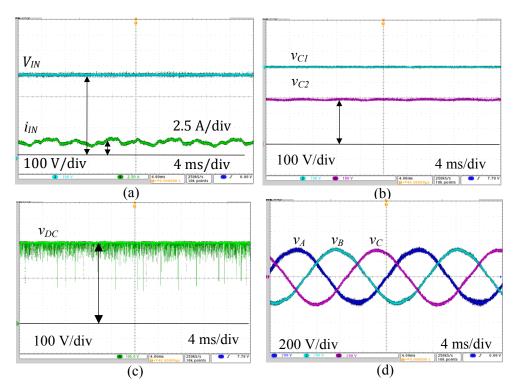

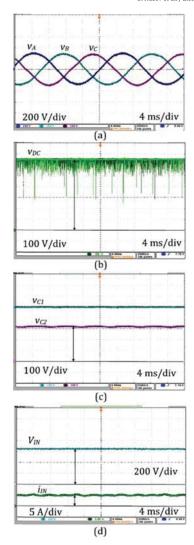

| Fig. 3.27. Experimental waveforms for the first point in buck mode without                              |       |

| third harmonic injection. a) Input current and voltage. b) Capacitor voltages. c)                       | 0.2   |

| dc-link voltage. d) Output voltage                                                                      | . 82  |

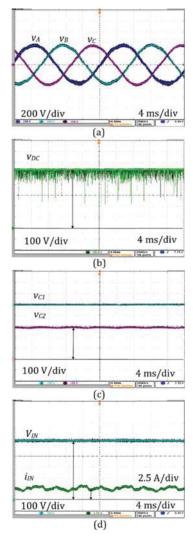

| Fig. 3.28. Experimental waveforms for the second point in buck mode with third harmonic injection. a) Input current and voltage. b) Capacitor voltages. c) |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| dc-link voltage. d) Output voltage                                                                                                                         | 83  |

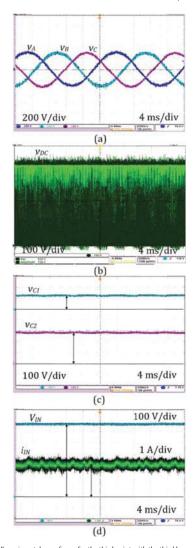

| Fig. 3.29. Experimental waveforms for the third point in boost mode with third                                                                             | 83  |

| harmonic injection. a) Input current and voltage. b) Capacitor voltages. c) de-                                                                            |     |

|                                                                                                                                                            | 84  |

| link voltage. d) Output voltageFig. 4.1. Control methods of dc-link voltage. a) Indirect. b) Direct                                                        |     |

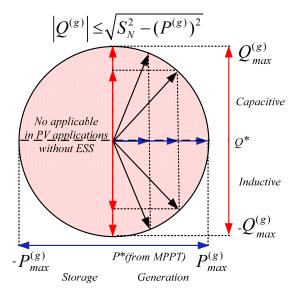

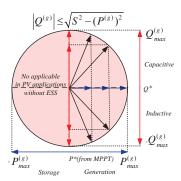

| Fig. 4.2. PV inverter regulation capacity                                                                                                                  |     |

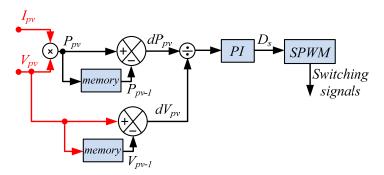

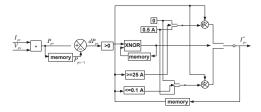

| Fig. 4.3. Implementation scheme of $dP/dV$ MPPT method.                                                                                                    |     |

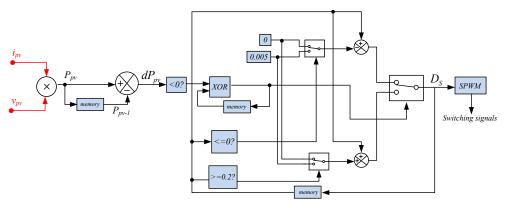

| Fig. 4.4. Implementation scheme of the P&O method.                                                                                                         | 88  |

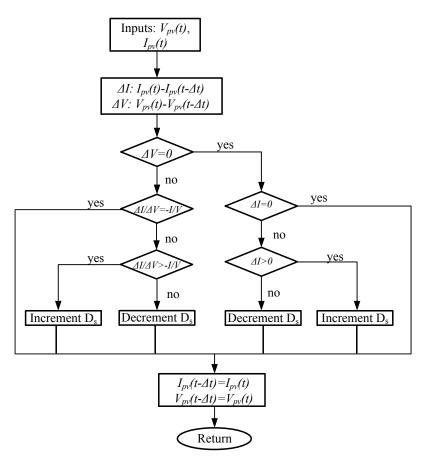

| Fig. 4.5. Incremental conductance flowchart.                                                                                                               |     |

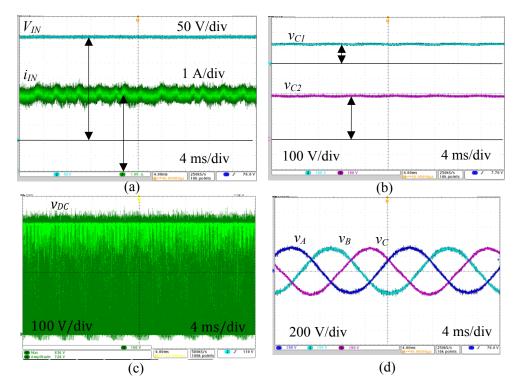

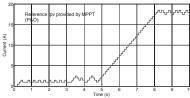

| Fig. 4.6. Evolution of transferred power and $D_s$ during a step in irradiance. a)                                                                         |     |

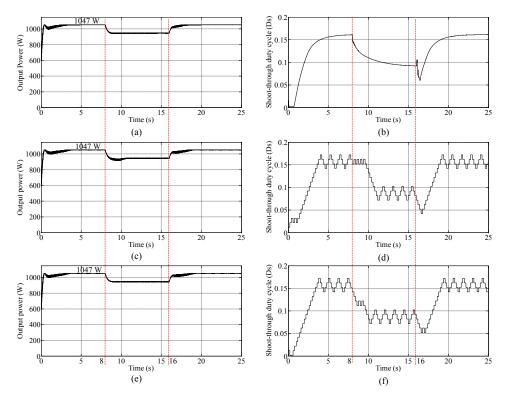

| and b) $dP/dV$ method. c) and d) P&O method. e) and f) InC method                                                                                          | 90  |

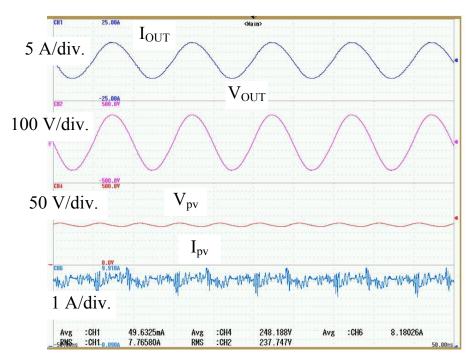

| Fig. 4.7. Experimental results at the MPP operation. From top to bottom:                                                                                   |     |

| output current, output voltage, input PV voltage and input PV current                                                                                      | 91  |

| Fig. 4.8. Operation strategy based on $\delta$ and $M$ as manipulated variables                                                                            |     |

| Fig. 4.9. <i>d-q</i> axes control sketch of the grid-connected inverter.                                                                                   |     |

| Fig. 4.10. Schematic of experimental power stage and setup configuration.                                                                                  |     |

| Fig. 4.11. Experimental configuration for testing the operation strategy in a                                                                              | 90  |

| traditional inverter.                                                                                                                                      | 96  |

| Fig. 4.12. Experimental results with control strategy based on <i>d-q</i> reference                                                                        | 90  |

| frame. a) Active power evolution. b) Reactive power evolution                                                                                              | 97  |

| Fig. 4.13. Power stage of the grid-connected PV system based on a single-                                                                                  | 7 1 |

| phase 3L-NPC qZSI.                                                                                                                                         | 98  |

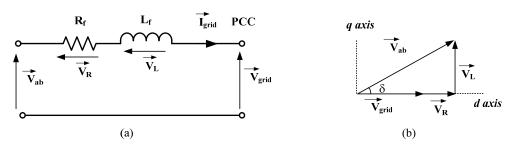

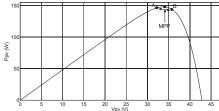

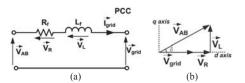

| Fig. 4.14. a) PCC equivalent scheme. b) Vector diagram.                                                                                                    |     |

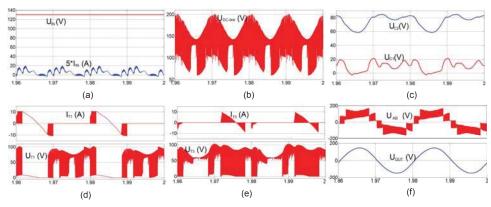

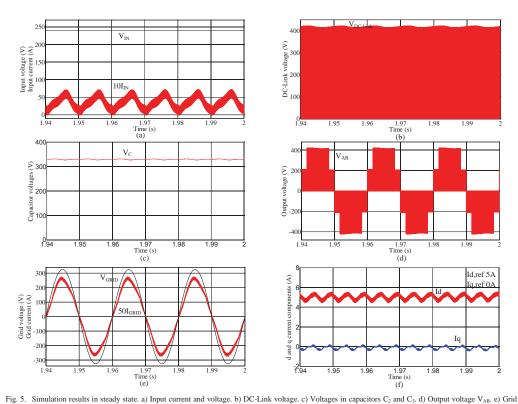

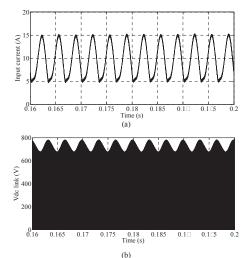

| Fig. 4.15. Simulation of main waveforms. a) Input current and voltage. b) dc-                                                                              | ))  |

| link voltage. c) Output voltage before filtering. d) Output current and grid                                                                               |     |

|                                                                                                                                                            | 101 |

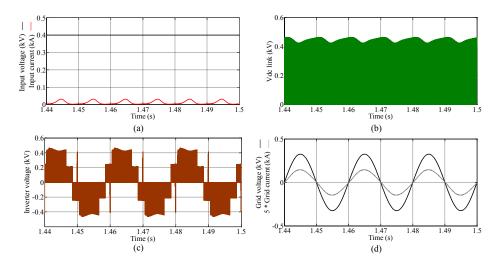

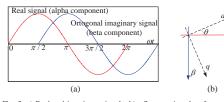

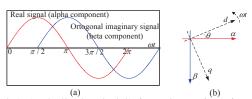

| Fig. 4.16. a) Real and imaginary signals. b) $\alpha$ - $\beta$ to rotating $d$ - $q$ reference frame                                                      | 101 |

|                                                                                                                                                            | 102 |

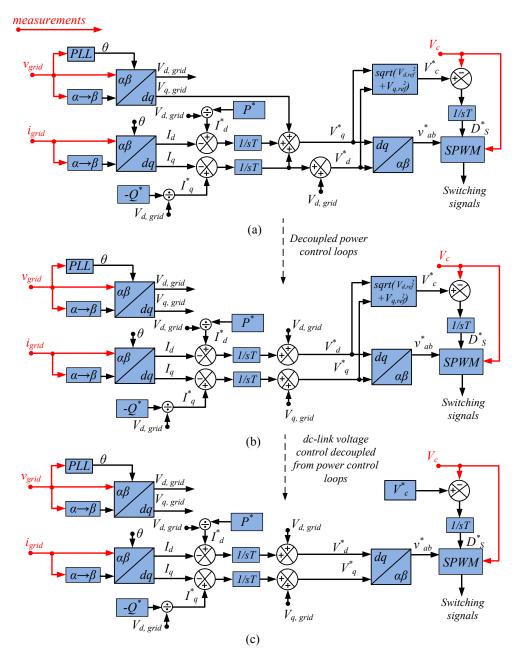

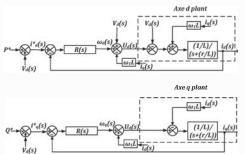

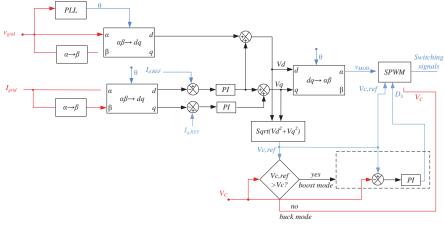

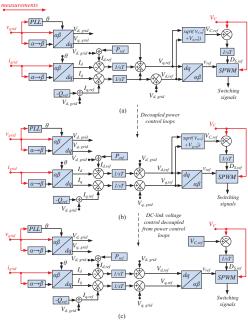

| Fig. 4.17. Proposed control schemes. a) Coupled power control loops and                                                                                    | 102 |

| coupled dc-link voltage control b) Decoupled power control loops. c)                                                                                       |     |

| Decoupled dc-link voltage control.                                                                                                                         | 104 |

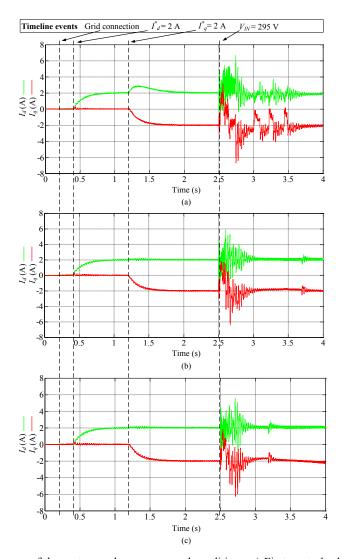

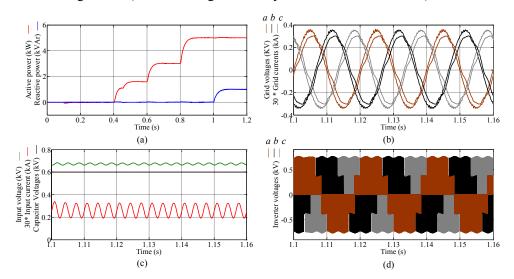

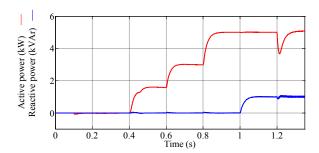

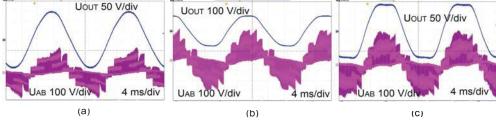

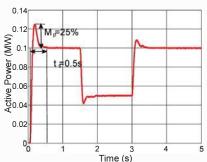

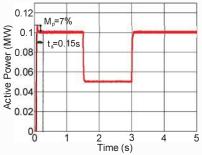

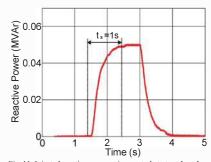

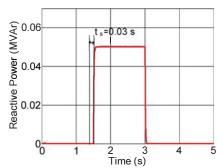

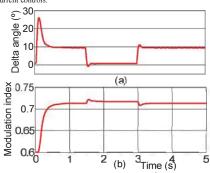

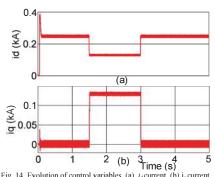

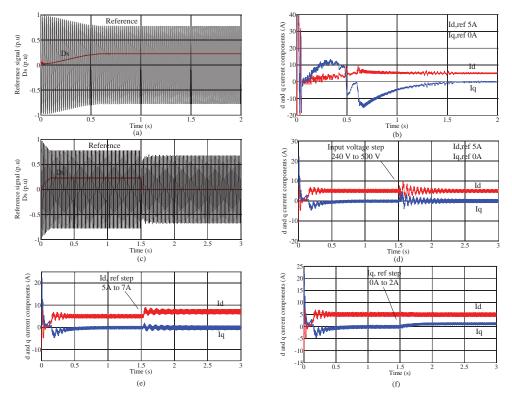

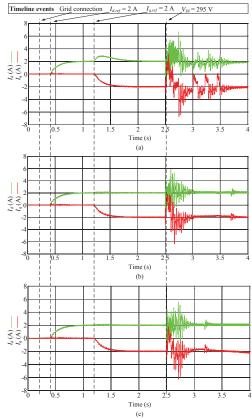

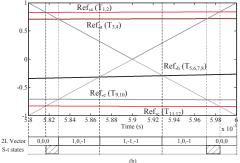

| Fig. 4.18. Responses of the system under programmed conditions: a) First                                                                                   | 107 |

| control scheme. b) Second control scheme. c) Third control scheme.                                                                                         | 106 |

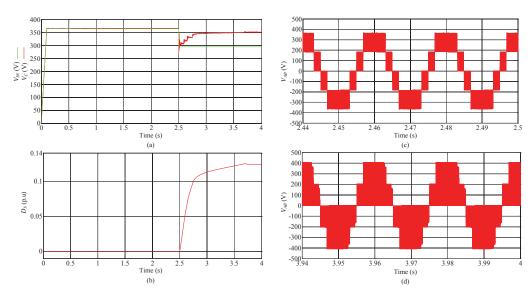

| Fig. 4.19. Different magnitudes obtained with the second control scheme: a)                                                                                | 100 |

| input voltage and capacitor voltage. b) Output voltage without ST. c) $D_s$                                                                                |     |

|                                                                                                                                                            | 107 |

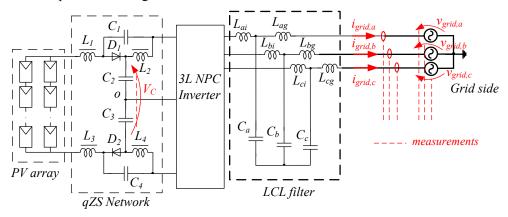

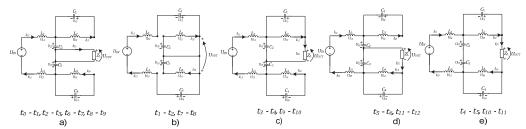

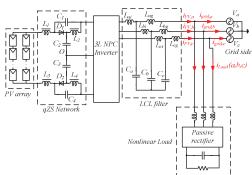

| Fig. 4.20. Case of study. Schematic circuit of a grid-connected three-phase 3L-                                                                            | 107 |

| NPC-qZSI in PV application.                                                                                                                                | 107 |

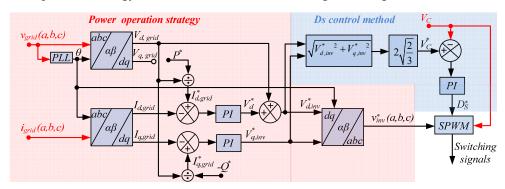

| Fig. 4.21. Power operation strategy and the proposed ST control method for                                                                                 | 107 |

|                                                                                                                                                            | 108 |

| r                                                                                                                                                          |     |

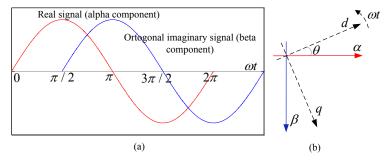

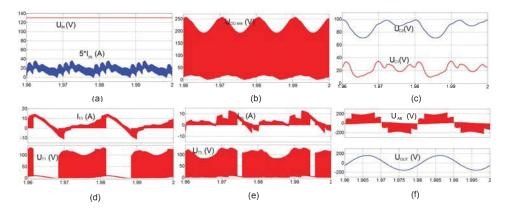

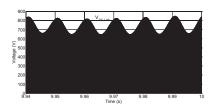

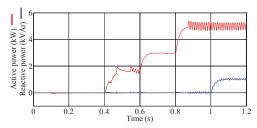

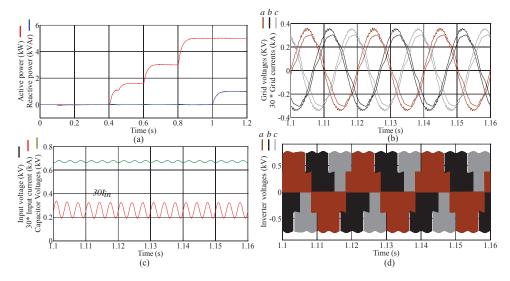

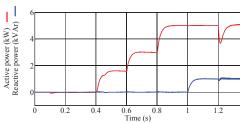

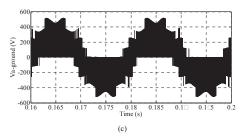

| Fig. 4.22. Main waveforms with shoot-through operation. a) $P$ and $Q$                       |

|----------------------------------------------------------------------------------------------|

| responses under different reference values. b) Steady waveforms of $v_{grid}$ and            |

| $I_{grid}$ . c) Steady waveforms of $I_{in}$ , $V_{in}$ and $V_c$ (boost is seen). d) Steady |

| waveforms of $v_{inv}$ (with shoot-through switching states)                                 |

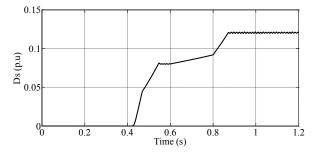

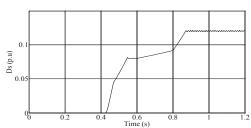

| Fig. 4.23. D <sub>s</sub> evolution                                                          |

| Fig. 4.24. System response during a step in input voltage                                    |

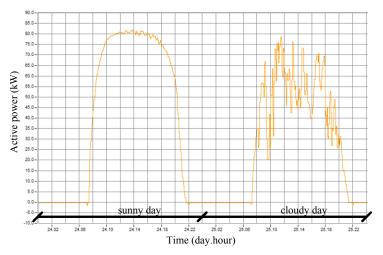

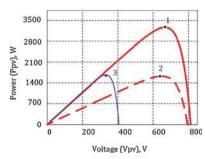

| Fig. 4.25. Measured PV generation curve in a sunny and cloudy days111                        |

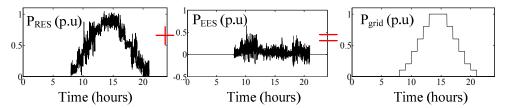

| Fig. 4.26. Power balance between RES, ESS and grid                                           |

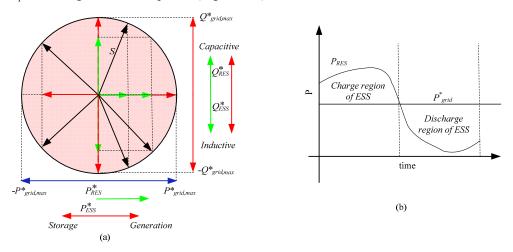

| Fig. 4.27. a) Active and reactive power distribution between RES and ESS. b)                 |

| Active power distribution between PV generation and battery                                  |

| charge/discharge. 112                                                                        |

| Fig. 4.28. First integration possibility of energy storage battery cells                     |

| Fig. 4.29. Second integration possibility of the energy storage battery cells                |

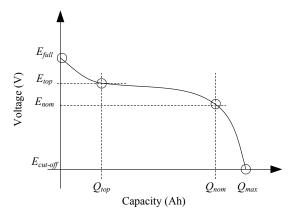

| Fig. 4.30. Typical discharge curve.                                                          |

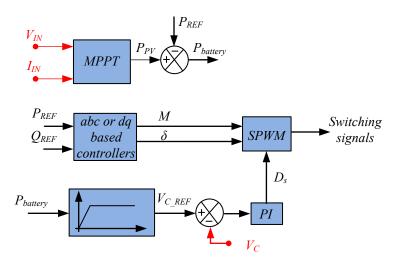

| Fig. 4.31. Sketch of the simplified control strategy for charge/discharge control 114        |

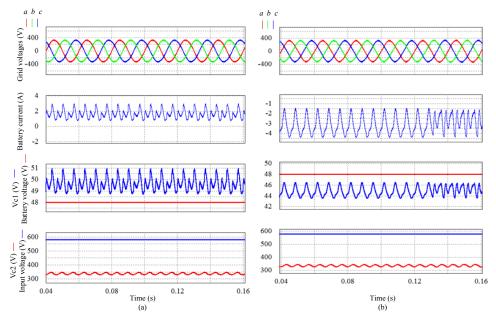

| Fig. 4.32. a) Main waveforms in the charging mode. b) Discharging mode                       |

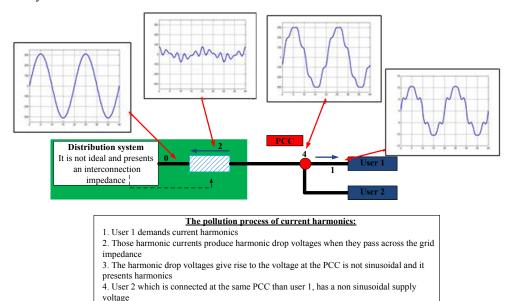

| Fig. 4.33. Voltage distortion process caused by harmonic loads                               |

| Fig. 4.34. Schematic of the studied case                                                     |

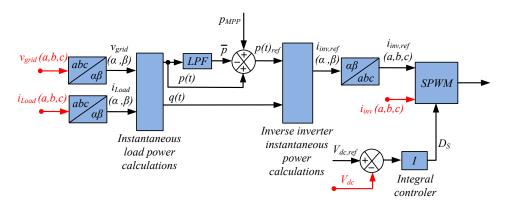

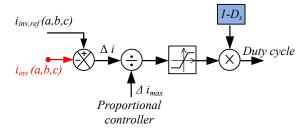

| Fig. 4.35. Block diagram of the proposed control strategy                                    |

| Fig. 4.36. Block diagram of duty cycle generation                                            |

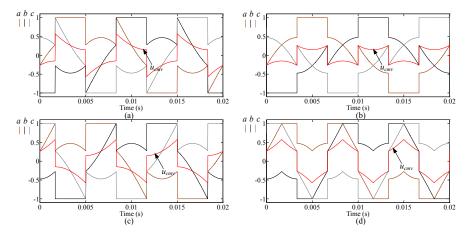

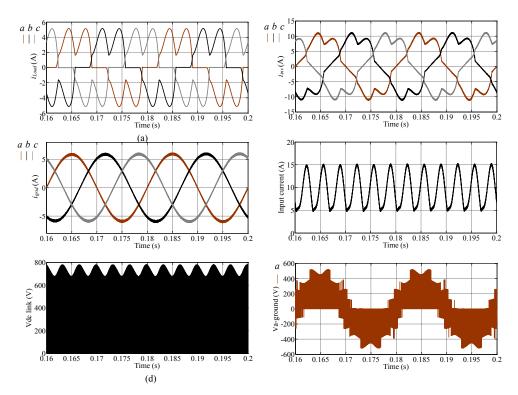

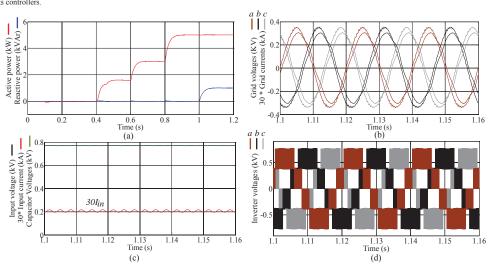

| Fig. 4.37. a) Current demanded by the load. b) $i_{inv}$ $(a,b,c)$ with non-active,          |

| reactive power compensation and MPP power higher than power demanded by                      |

| the load. c) $i_{grid}$ $(a,b,c)$ that flows to the grid. d) Input current. e) dc-link       |

| voltage. f) Voltage between the middle point of branch a and the ground                      |

# **List of Tables**

| Table 2.1. Half-bridge switching and conduction states.                                | 17           |

|----------------------------------------------------------------------------------------|--------------|

| Table 2.2. H-bridge switching states                                                   | 19           |

| Table 2.3. Two-level three-phase VSI switching states.                                 | 21           |

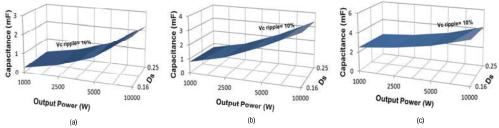

| Table 2.4. System parameters of single-phase prototype                                 | 47           |

| Table 2.5. System parameters of three-phase prototype.                                 |              |

| Table 3.1. Summary of different PWM control method expressions as function of M        | <i>1</i> .61 |

| Table 3.2. Main parameter from the panel datasheet.                                    | 81           |

| Table 3.3. Values in each selected operation point.                                    | 81           |

| Table 4.1. Summary of MPPT algorithm based on P&O                                      | 88           |

| Table 4.2. Simulation parameters                                                       | 90           |

| Table 4.3. Electrical setup and control system parameters.                             | 97           |

| Table 4.4. Variables involved in the first control strategy for single-phase topology. | 99           |

| Table 4.5. Values for the simulation study                                             | . 105        |

| Table 4.6. Main parameters for the simulation study                                    | . 109        |

### **Nomenclature**

- a mathematical operator for abc to  $\alpha$ - $\beta$  transformation

- ac alternating current

- $A_{ac}$  amplitude of  $y_{ac}$

- $A_{dc}$  amplitude of  $x_{dc}$

- ANPC Active NPC

- APF Active power filter

- APOD Alternative Phase Opposition Disposition

- B Boost factor

- CCM Continuous Conduction Mode

- $C_f$  Capacitance of the output filter

- CHB Cascaded H-Bridge

- $C_i$  Capacitor

- CMC Cascade Matrix Converter

- CPWM Continuous Pulse Width Modulation

- CSI Current Source Inverter

- C<sub>st</sub> ST carrier

- $D_A$  duty cycle of the active states

- dc direct current

- DCLC DC-Link Cascaded

- DCM Discontinuous Conduction Mode

- $D_i$  General diode

- DG Distributed Generator

- DPWM Discontinuous Pulse Width Modulation

- DPWMMAX Discontinuous Pulse Width Modulation that the MAXimum signal defines the zero sequence

- DPWMMIN Discontinuous Pulse Width Modulation that the MINimun signal defines the zero sequence

- D<sub>s</sub> Shoot-through Duty Cycle

- $D_s^*$  Reference Shoot-through Duty Cycle

- $D_Z$  duty cycle of the zero states

- $\bar{D}_s$  Average  $D_s$

- EI Edge Insertion

- ESS Energy Storage System

- f frequency

#### Nomenclature

- FB Full Bridge

- FC Flying Capacitor

- $f_{res}$  resonance frequency

- $f_{sw}$  switching frequency

- $f_l$  line frequency

- G Voltage gain

- GTO Gate Turn-Off Thyristor

- H-NPC Neutral-point-Clamped and H-Bridge

- $h_{sw}$  switching harmonic order

- HV-IGBT High Voltage IGBT

- IGBT Isolated Gate Bipolar Transistor

- IGCT Integrated Gate-Commutated Thyristor

- InC Incremental Conductance

- $I_{grid}$  Reference grid current

- I<sub>sc</sub> Short circuit current

- I<sub>MPP</sub> Maximum power point current

- $I_{OUT}$  Output current

- $I_{\underline{d}}$  d component of the output current

- $I_d^*$  d component of the reference output current

- $I_q$  q component of the output current  $I_q^*$  q component of the reference output current

- $I_{pv}$  Photovoltaic current

- $i_a$  output current

- $i_{Ci}$  instantaneous current across a capacitor

- $i_{DC}$  Output current at low frequency

- $i_{DC\_Max}$  Peak value of the output current at low frequency

- $i_{grid}(t)$  instantaneous injected current

- Reference injected current vector to the grid

- $i_{in}$  input current

- $i_{LI}$ ~ ac component of the input current

- $\hat{i}_{li}$  peak value of the current in the inductance

- k number of output voltage level

- $K_{CI}$  voltage ripple factor in  $C_I$

- $K_{C2}$  voltage ripple factor in  $C_2$

- $K_{CLI}$  Low frequency voltage ripple factor for capacitors  $C_I$  and  $C_4$

- $K_{CL2}$  Low frequency voltage ripple factor for capacitors  $C_2$  and  $C_3$

- $K_L$  Predefined ripple in the inductor current

- $K_{LHI}$  High switching frequency current ripple factor

- $K_{LLI}$  Low frequency input current ripple factor

- $K_{LL2}$  Low frequency current ripple factor for inductors  $L_2$  and  $L_4$

- K<sub>i</sub> Integral constant of PI controller

- K<sub>p</sub> Proportional constant of PI controller

- L weighted inductance

- LCCT-qZSN Inductor-Capacitor-Capacitor-Transformer qZSN

- LCI Load Commutated Inverter

- $L_f$  Inductance of the output filter

- $L_g$  grid inductance

- $L_i$  Inductance i

- $L_{\rm i}$  inverter inductance

- $m_f$  frequency modulation index

- *M* Modulation index

- MBC Maximum Boost Control

- MCBC Maximum Constant Boost Control

- ML MultiLevel

- MLI MultiLevel Inverter

- MMC Modular Multilevel Inverter

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- MPP Maximum Power Point

- MPPT Maximum Power Point Tracking

- MR<sub>i</sub> Modified reference signal

- MToe Million Tonnes of oil equivalent

- MTBF Mean Time Between Failures

- MTTF Mean Time to Failures

- *n* turns ratio

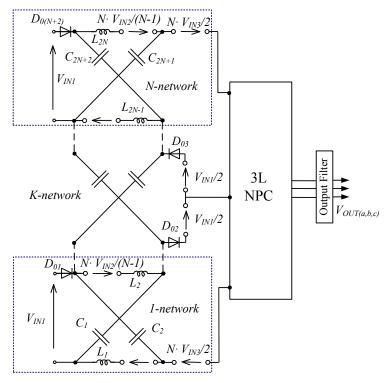

- N Number of cascaded impedance networks

- NPC Neutral-Point-Clamped

- NPC-CHB Neutral-Point-Clamped and Cascaded H-Bridge

- N<sub>p</sub> Parallel connected PV panels

- N<sub>s</sub> Series connected PV panels

- NTV Nearest Three Vector

- P Active power

- $P^{(g)}$  Generated active power

- PCC Point of Common Coupling

- PD Phase Disposition

- PI Proportional-integral controller

- $P_{IN}$  Input power

- POD Phase Opposition Disposition

- $P_{OUT}$  Output power

- PSC Phase Shifted Carrier

- PV Photovoltaic

- PWM Pulse-Width-Modulation

- $P^*$  Reference Active Power

- P&O Perturb and Observe

- qZSI quasi-Impedance-Source Inverter

- qZSN quasi-Impedance-Source-Network

- Q Reactive power

- $Q^{(g)}$  Generated reactive power

- $Q^*$  Reference Reactive Power

- r index that relates  $L_g$  and  $L_i$

- R resistance

- $R_f$  resistance of the L filter

- RCM Reduced Common Mode

- REC Reduced Element Count

- Ref<sub>i</sub> Reference signal *i*

- RES Renewable Energy Sources

- R<sub>G</sub> Gate Resistor

- S Apparent power

- SBC Simple Boost Control

- SHE Selective Harmonic Elimination

- SIDER Smart Inverter for Distributed Energy Resources

- SL-qZSN Switched Inductor quasi-Impedance-Source-Network

- ST Shoot-Through switching states

- $S_{Ti}$  Binary gate signal of  $T_i$

- $S_{Tx}$  Binary gate signal of top switch of branch x

- SVC Space Vector Control

- SVPWM Space Vector PWM

- $t_A$  time duration of the active states

- *t<sub>S</sub>* time duration of the shoot-through states

- $t_Z$  time duration of the zero states

- T Temperature

- T fundamental period

- T<sub>i</sub> Constant time of the integral controller

- THD<sub>I</sub> current Total Harmonic Distortion

- THD<sub>U</sub> voltage Total Harmonic Distortion

- THIPWM Sinusoidal PWM with the Third Harmonic Injection

- $T_i$  General semiconductor switch

- $T_0$  ST time interval

- TPES Total Primary Energy Supply

- Trans-qZSN qZSN with two coupled inductor

- $T_{sw}$  switching period

- T<sub>on</sub> Conduction time in semiconductor

- $T_{sw}$  Switching period

- $\vec{u}$  unitary vector in direction of  $\vec{l}_{ab}$

- $u_{cmv}$  common mode voltage

- $u_d$  unitary vectors in the d direction

- $u_q$  unitary vectors in the q direction

- $v_{ab}^*$  Reference output voltage between branches

- $v_{ab}$  output voltage between branches

- $v_{ao}$  output voltage between middle point of branch a and neutral point

- $v_{a,ref}$ ,  $v_{b,ref}$  and  $v_{c,ref}$  References or modulating signals

- $v_{gen}(t)$  instantaneous generator voltage

- $v_{pcc}(t)$  instantaneous PCC voltage

- $v_{Li}$  instantaneous voltage across an inductance

- $v_n$  bottom ST envelope

- $v_{nl}$  First bottom ST envelope in MCBC

- $v_{n2}$  Second bottom ST envelope in MCBC

- $v_p$  upper ST envelope

- $v_{pl}$  First upper ST envelope in MCBC

- $v_{p2}$  Second upper ST envelope in MCBC

- $v_{xn}$  output voltage between middle point of branch and neutral point of the

- $V_{AB}$  average output voltage between branches

- $\vec{l}_{ab}$  Reference output voltage vector of the fundamental component in terminals of the 3L-NPC-qZSI

- $V_{ab}^*$  Reference RMS output voltage of the fundamental component in terminals of the 3L-NPC-qZSI

- $V_{d}^{*}$  reference value of the dc link voltage  $V_{d}^{*}$  d component of the reference output voltage

- $V_q^* q$  component of the reference output voltage

- $\vec{l}_{i}$  Reference voltage drop vector in the filter inductance

- $V_I^*$  Reference RMS voltage drop in the filter inductance

- $V_R^*$  Reference RMS voltage drop in the resistance of the filter inductance

- $\vec{l}_R$  Reference voltage drop vector in the resistance of the filter inductance

- $\vec{l}_{grid}$  Voltage grid vector

- $V_{Ci}$  average voltage across the capacitors over one switching period

- $V_{dc}$  dc voltage source

- $V_g$  RMS grid voltage value

- $V_{gen}$  RMS voltage at the terminal of generator  $V_i(h_{sw})$  output voltage at the switching frequency

- $V_{inv}$  RMS fundamental component of line-to-neutral inverter voltage

- $V_{IN}$  input voltage source

- $V_{Li}$  average voltage across an inductance

- V<sub>MPP</sub> Maximum power point voltage

- Voc Open Circuit Voltage

- $V_{vv}$  Photovoltaic voltage

#### Nomenclature

- $V_{pv}^{*}$  Reference photovoltaic voltage  $V_{pcc}$  RMS voltage at the PCC

- $v_{pcc,i}$  instantaneous voltage at the PCC in phase i

- $V_{OUT}$  Output voltage

- $V_s$  Boosted voltage

- VSI Voltage Source Inverter

- V2G Vehicle to Grid

- $\hat{v}_{ac}$  peak value of the phase-to-neutral output voltage

- $v_{Ci} \sim$  ac voltage component of the capacitor i

- $\hat{v}_{c_1} \sim$  peak value of the ac voltage component of the capacitor i

- W Solar irradiance

- $x_{dc}$  dc variable

- $y_{ac}$  ac variable

- $Z_{gen}$  Reactance of the generator

- ZSI Impedance-Source Inverter

- ZSN Impedance-Source-Network

- $\Delta V_{c1}$  Voltage ripple in  $C_1$  $\Delta V_{c2}$  Voltage ripple in  $C_2$

- $\delta$  Angle between  $V_{gen}$  and  $V_{pcc}$

- $\theta$  phase

- $\theta_{grid}$  Grid phase

- $\omega_I$  fundamental pulsatance

- 2L Two-Level

- 3L Three-Level

- 3L-NPC-qZSI Three-Level Neutral-Point-Clamped quasi-Impedance-Source Inverter

# Chapter 1 Introduction

### 1.1 Photovoltaic energy injection into the grid

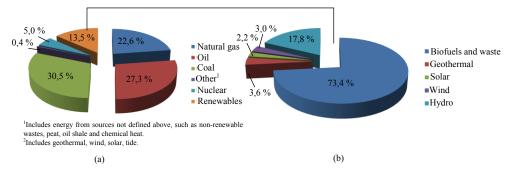

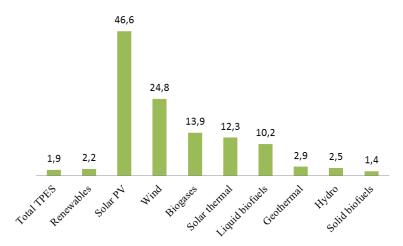

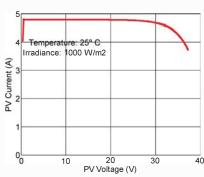

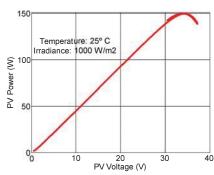

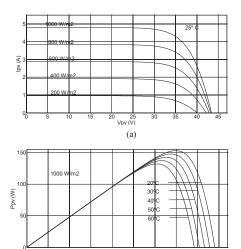

World Total Primary Energy Supply (TPES) was 13555 Million Tonnes of oil equivalent (MToe) in 2013, where its 13.5 % (1829 MToe) was generated from Renewable Energy Sources (RES) as Fig. 1.1 a) represents. Solid biofuels (excluding wastes) is the largest renewable energy source, representing 10.4 % of world TPES and 73.4 % of global renewables supply as Fig. 1.1 b) depicts. Hydroelectric power is the second largest source, providing 2.5 % of world TPES and 17.8 % of renewables. Geothermal, liquid biofuels, biogases, solar, wind, and tide each represent a smaller share and make up the rest of the renewable energy supply. Growth of solar photovoltaic and wind power have been especially high during the last years, which grew at average annual rates of 46.6 % and 24.8 %, respectively (see Fig. 1.2) [1].

Fig. 1.1. a) 2013 fuel shares in world total primary energy supply. b) 2013 product shares in world renewable energy supply.

Fig. 1.2. Annual growth rates of world renewable supply from 1990 to 2013.

Lack of conventional energy sources and concern about environmental pollution are some of the reasons of this significant growth. As an important challenge, the target of the European Union is to reach 20 % of energy production by RES in 2020.

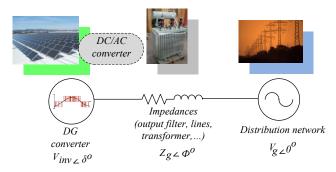

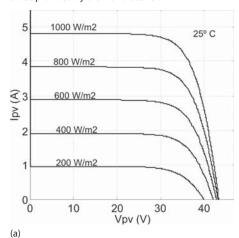

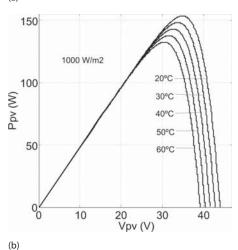

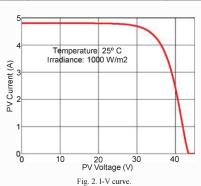

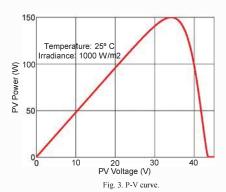

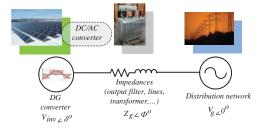

In the case of photovoltaic (PV) energy we can distinguish between grid-connected system and off-grid installation. In the first case, there are several possible typologies according to the inverter configuration (central, string or module), to the number of energy conversion stages and to the existence of transformer: transformer-based (at the high or at the low frequency side) or transformer-less. Fig. 1.3 schematically shows grid-connected photovoltaic installations.

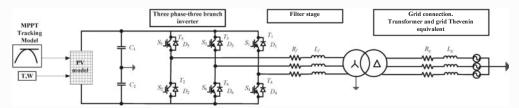

Fig. 1.3. General scheme of a grid-connected photovoltaic system.

The photovoltaic inverter is the key element in grid integration of PV systems because it enables the efficient and flexible interconnection of different elements to the electric power system. Aforementioned reasons have produced a fast rise in the number of inverter-based Distributed Generators (DG) connected to the low-voltage distribution

network. Hence the inverter will be a major player in future distributed power system scenarios based on smartgrid and microgrid concepts.

For a long time, PV inverters' function was merely to inject power into the main grid with a unitary power factor as the control reference [2] but, under new trends and policies for PV plants, they are integrated as active and smart devices. In this way, PV inverters would be able to contribute to the local voltage support, to improve the power quality and to give rise to flexibility and security of supply. Some of those new demands for inverters are power flow controls [3], voltage level restoration at the Point of Common Coupling (PCC) [3]-[5], active filtering capabilities [5], integration with energy storage systems [6] and communications compatibilities [7].

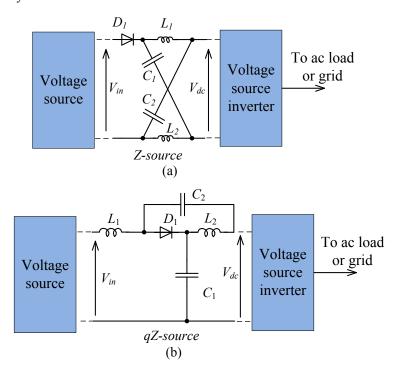

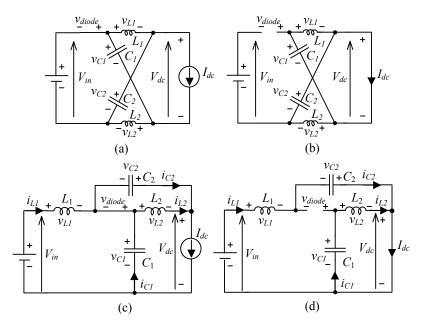

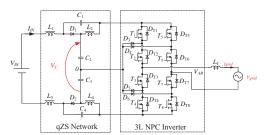

Due to the high cost of solar energy (although the cost of PV panels have dropped during 2008 by around 40 % to levels under € 2/W), industry and research are aiming at cost reductions and enhanced performance of the energy conversion process, with a focus on the inverter topologies. The inverter is traditionally characterized by two-stage converters composed by a dc-dc boost converter and the Voltage Source Inverter (VSI) but, innovative ideas in terms of inverter circuitries have emerged during the last years. Some of them seem quite suitable for PV applications because they can step up the dc input voltage in a single power conversion stage by means of shoot-through (ST) switching states. They are known as Z-Source Inverters (ZSI) [8], quasi-Z-Source Inverters (qZSI) [9] and its derivations [10]. The ZSI/qZSI fulfils buck/boost capability in single-stage topology and overcomes the limits of traditional VSIs. Hence, high reliability, high efficiency, large operation range and low cost can be achieved.

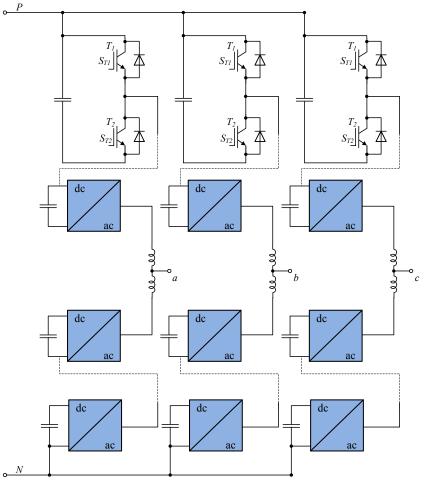

Furthermore, ZSI family has been integrated with multilevel inverter (MLI) bridges [11] to acquire their intrinsic advantages such as lower semiconductor voltage stress, lower required blocking voltage capability, decreased dv/dt, better harmonic performance, soft switching possibilities without additional components and higher switching frequency due to lower switching losses, among others.

However, because of the relatively early stage, only few studies deal with the grid-connected integration with closed loop control systems, which basically must provide coexistence of an operation strategy of the inverter, a Maximum Power Point Tracking (MPPT), a dc-link voltage control method and a special modulation technique to embed the shoot-through states into the normal ones.

#### 1.2 Thesis motivation

This thesis is a part of the research project dealing with the development of new concept of photovoltaic inverters called "Smart Inverter for Distributed Energy Resources (SIDER)", launched in 2006 by University of Extremadura. This project, supported by the Spanish Government, was divided into three subprojects that were carried out by the University of Extremadura, University of Córdoba and University of Cádiz. The different subprojects dealt with subjects regarding power control and quality through

the power electronic devices, communication between different grid-connected devices to develop new protection systems (special mention is on islanding detection) and signal processing for the detection and characterization of disturbances.

Focusing on the subproject developed by University of Extremadura, attention was paid in the design and development of an inverter with the necessary topology, elements, control strategy, tracking technique and switching signal generation to provide this new equipment with the characteristic to become a SIDER. It is interesting to highlight two main functionalities that were implemented: 1) control of the voltage at the point of common coupling (both the fundamental component and the harmonics) and 2) generation planning, trying to change the consideration of the power plant from non-manageable to quasi-manageable (by using energy storage system).

During the development of this project, the possibility of getting a strategic collaboration with Tallinn University of Technology raised up in 2012, with the main objective of exploring new inverter topologies devoted to photovoltaic applications since the cost reduction and enhanced performance of the energy conversion process are requested. These specific research activities were supported by the project SIDER (TEC2010-19242-C03.01) and the grant (BES-2011-043390) from the Ministry of Economy and Competitiveness from Spain, the project (SF0140016s11) and the grants (ETF8538 and ETF8687) from Estonian Ministry of Education and Research and the grant (COST ACTION MP1004) from European Union.

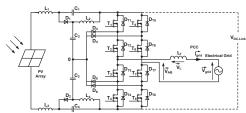

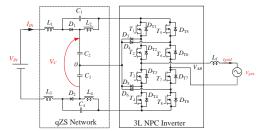

From the technical point of view, this research lies in the new single stage inverter topologies, suitable for PV applications since they have intrinsic advantages. In the project SIDER the solution was based on a traditional topology, hence new and further functionalities would appear. As a result, a new topology called "Three-Level Neutral-Point-Clamped quasi-impedance Source Inverter" (3L-NPC-qZSI) both in single phase and in three phase systems is proposed and validated experimentally, trying to get the advantages of both qZS Networks (qZSN) and multilevel bridges. Besides a new modulation technique to generate the Shoot-Through (ST) switching signals and different control strategies are investigated to increase the overall performance of the photovoltaic energy conversion process.

### 1.3 Objectives of the thesis

The main goal of the PhD research is to develop a new single stage inverter topology for PV applications, its modulation technique and control algorithms to improve the traditional solutions.

The objectives of the PhD research are classified into two categories: general (related to the PhD student education) and specific ones (related to the topic of dissertation):

### General objectives

- To go in depth and to extend the acquired knowledge during the development of the SIDER project.

- To maintain and to reinforce the research collaboration with foreign universities.

- To increase the skills and experience of the PhD student and his research group.

- To generate new useful knowledge and to publish the results in specific journals

- To share the new developments and proposals to the industry.

- To define directions for future research and international research projects.

### Specific objectives

- To analyse and classify the current state-of-the-art and trends both in single stage buck/boost multilevel inverters and in their modulation techniques.

- To propose, to size and to validate a new single stage buck/boost multilevel inverter and a new modulation technique.

- To develop different control strategies for this new inverter for photovoltaic applications in grid-connected mode for it to behave as an active device.

#### 1.4 Structure of the thesis

The framework of this PhD thesis is divided into 5 chapters and 1 appendix.

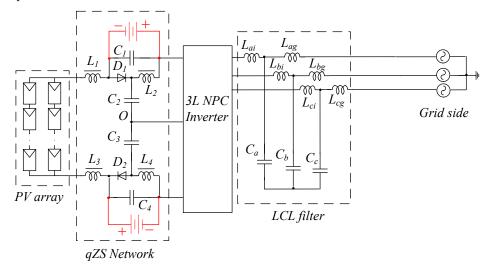

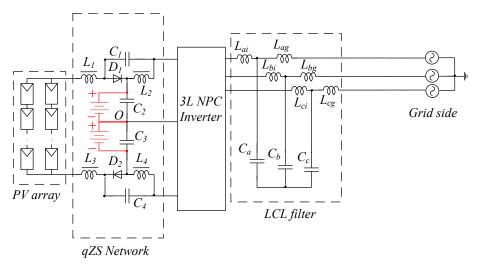

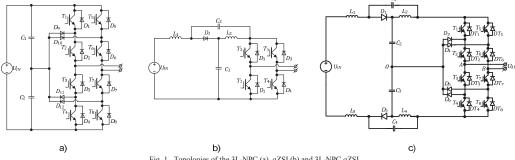

Chapter 2 summarizes and covers the different alternatives of the VSI topologies. Starting from the different basic two-level traditional solutions for single phase and three-phase applications, the review and description of the two-level inverter based on impedance-Source-Network (ZSN), qZSN and its derived network are presented with the focus of the boost operation in a single stage. Subsequently some of the well-known multilevel bridges are classified and presented, in order to identify their main features and advantages such as an improved quality of the voltage waveform and the optimization of the power switches among others. Then, a deep review of the multilevel buck/boost inverter reported in the literature is described because they inherit the advantages of inverters based on ZSN and multilevel configurations. Finally and starting from the aforementioned basis, it is possible to test the new proposed 3L-NPC-qZSI. The passive element sizing in both the power switching devices and the output filter are explained to demonstrate how the prototypes were assembled.

Chapter 3 deals with the basics of the switching signal generation or modulation techniques. At the beginning, the traditional sinusoidal Pulse-Width-Modulation (PWM) or carrier based methods for two-level single-phase and three-phase VSIs are described. In this last case the continuous and discontinuous pulse-width-modulation are distinguished, depending on the zero sequence voltage. Then, a classification of multilevel

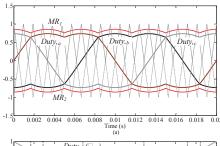

modulation methods as extension of the two-level is depicted. Right after it, the most common modulation techniques oriented to two-level inverter based on ZSN are explained. These ones have a main particular feature, an additional state called the shoot-through state, which produces the simultaneous conduction of switches of the same phase branch to boost the input voltage. According to the voltage gain or boost factor, the simple boost control, the maximum constant boost control and the maximum boost control are compared. Finally, a deep and updated review of the modulation methods for multilevel impedance source inverters (based on sinusoidal pulse-width-modulation or space vector modulation) allows understanding the new proposed techniques both in single phase and in three phase configuration. Their principle of operation is explained in detail and experimentally validated.

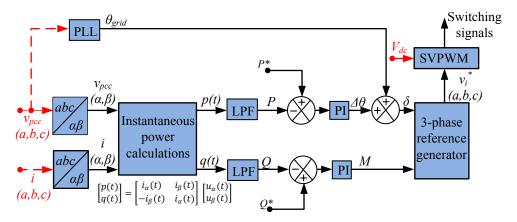

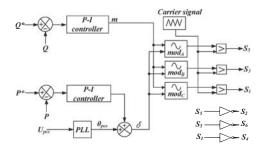

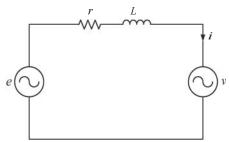

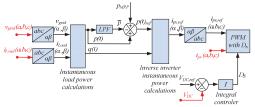

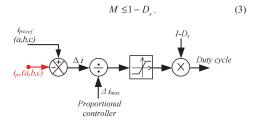

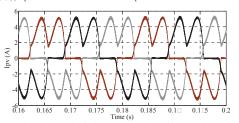

Chapter 4 is intended to the operation strategies for performing grid-connected active functions for the new proposed "three-level neutral-point-clamped quasi-impedance source inverter". Based on mature control strategies for traditional grid-connected inverters, several new control strategies based on closed control loops along with different dc-link voltage control loops have been developed and explained. The first operation functionality is devoted to regulate the injected active and reactive power into the electrical grid, where different approaches were taken into account as well as the maximum power point tracking algorithm. Then its integration with energy storage system is presented and discussed for a better management of the active power between the photovoltaic plant, the storage system and the grid. Finally the capability of this new inverter to develop active filtering functions is studied, and a new control strategy is derived from the traditional approaches.

Chapter 5 summarizes the key results that have been obtained during the research and the possible continuations or future research works are highlighted.

Since the PhD is based on the different papers that the author has published, Appendix contains the book chapters, journal papers and conference contributions directly connected to the topic of dissertation and they are considered as an extension or continuation of the different chapters. Some special citations to these publications are remarked during the chapters, providing further details about this PhD research.

#### 1.5 Results, novelties and dissemination

This section presents the most important findings obtained during the PhD research. As main scientific novelties, the following ones are highlighted:

- Analysis of the current state-of-the-art of the multilevel buck/boost inverter topologies.

- Analysis of the current state-of-the-art of the multilevel buck/boost inverter modulation techniques.

- Proposal, validation and assembly of a new topology for this family of converters, called "three-level neutral-point-clamped quasi-impedance source inverter" in single phase and three-phase version.

- Development and validation of new modulation techniques for this family of inverters that generate the traditional switching states and the ST states.

- Proposal and validation of new maximum power point tracking algorithms for this system.

- Development and proposal of new operation strategies based on different control variables to deliver active power and reactive power regulation and active filtering capabilities for this new inverter, to integrate it as active device into the electrical grid, along with dc-link voltage control methods.

The results obtained during the PhD research have been reported at 2 book chapters and published in 14 journal papers, in 15 international conferences and in 8 national conferences. 11 of the journal papers are published in journals included in the JCR list. The conference contributions were peer-reviewed and the majority of them are available in IEEE database. The most important papers directly connected to the topic of this PhD are listed and added in the Appendix. In addition, one co-authored patent application was submitted to the European patent office.

Concurrently, in terms of international collaboration of the University of Extremadura, this coordinate research has permitted the mobility and cooperation between different members of the group that the author belongs to, and members of Tallinn University of Technology (Estonia) and Aalborg University (Denmark) besides other European universities and institutions. It has also helped to apply for new collaborative and international projects in different calls for future research and development.

# Chapter 2 Three-Level NeutralPoint-Clamped qZSI Topology

## 2.1 Introduction

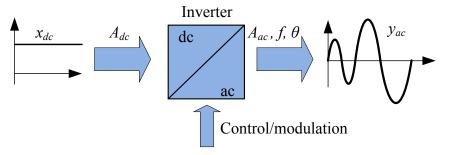

Power electronic converters that change dc voltages and currents to ac waveforms are known as inverters. Their main objective is to build, from one or multiple dc power supplies, an ac switched pattern output waveform, with a fundamental component with adjustable phase, frequency and amplitude to deal with a certain application. This concept is represented in Fig. 2.1, for a generic dc variable  $x_{dc}$ , normally current or voltage.  $A_{dc}$  represents a constant amplitude of  $x_{dc}$ . In the other side,  $A_{ac}$ , f and  $\theta$  are the adjustable amplitude, frequency and phase of the fundamental component of the switched ac variable  $(y_{ac})$ . This procedure is achieved by the proper control of the static power switches that interconnect the dc source to the ac load/grid, using the different configurations or conduction states provided by a certain topology.

Fig. 2.1. Principle of operation of an inverter.

The dc power supplies can be either current or voltage sources, dividing the inverter family into two main traditional groups: current source inverter (CSI) and VSI, as depicted in Fig. 2.2. This figure also classifies the different type of CSI and VSI topologies depending on their power range of application. On the one hand, CSI have dominated the medium-voltage high-power range with the PWM-CSI and the load-commutated inverter (LCI) [12]. On the other hand, VSIs are widely found in low-and medium- power applications with single-phase and three-phase two-level VSI. Finally, VSI has been also proposed as an attractive solution in the medium-voltage high-power range by means of multilevel topologies [13].

Fig. 2.2. Inverter topology traditional classification.

# 2.2 Two-level traditional VSI topologies

### 2.2.1 Single phase

Fig. 2.3 represents the half bridge, a) with IGBT and b) with MOSFET, considered as the basic two-level single-phase inverter. It is composed by one inverter leg or branch, containing two semiconductor switches ( $T_1$  and  $T_2$ ) and two freewheeling diodes ( $D_1$  and  $D_2$ ) to provide a negative current path through the switch when necessary. It also includes two capacitors to split the total dc link voltage and to provide a 0 V midpoint for the load (also known as neutral point). The load is connected between this node and the inverter leg output phase node a. P and N denote the positive and negative bus bars respectively. The dc voltage source (a battery, fuel cell, rectifier, PV panel, etc.) is represented by  $V_{dc}$ .

The switches are controlled by binary gate signals ( $S_{TI}$  and  $S_{T2}$ ) which can be 1 or 0, that represent the "on" or "off" state respectively. This control must be alternate to avoid simultaneous conduction of  $T_I$  and  $T_2$  since it would short-circuit the dc link. With a simple reasoning, it is easy to understand the deduced information in Table 2.1.

The fact that there are only two possible output voltages is why this VSI is known as two-level inverter.

Fig. 2.3. a) Half-bridge inverter topology with IGBT. b) With MOSFET.

Table 2.1. Half-bridge switching and conduction states.

| Switching state | Gate signal $(S_{TI})$ | Output voltage $(v_{ao})$ | Conduction state | Output current $(i_a)$ | Semiconductor conducting |

|-----------------|------------------------|---------------------------|------------------|------------------------|--------------------------|

| 1               | 1                      | $V_{dc}/2$                | (a)              | < 0                    | $D_I$                    |

|                 |                        |                           | (b)              | > 0                    | $T_I$                    |

| 2               | 0                      | $-V_{dc}/2$               | (c)              | > 0                    | $D_2$                    |

|                 |                        |                           | (d)              | < 0                    | $T_2$                    |

Other important feature to mention is that the commutation of a power devices is not instantaneous, hence a dead time has to be included before a switch-on, to avoid a simultaneous conduction between both switches. This dead time is just a little bit larger than the switch-off commutation (for IGBT, this values is around two micro seconds).

Although  $S_{TI}$  is a binary signal that generates two different states, there will be four different conduction states depending on the current polarity, which determines whether the power switches or the diodes are conducting. The four conduction states are represented in Fig. 2.4, where a hypothetical ac square-wave operation of the inverter feeding an inductive load is considered. Note that it does not illustrate a real current waveform for such voltage.

For semiconductor sizing considerations, while not conducting, the power switch is blocking the total  $V_{dc}$ . Therefore, this topology is more common in applications in the low voltage range.

Fig. 2.4. Half-bridge inverter conduction states when a)  $v_{ao} = V_{dc}/2$  and  $i_a < 0$ , b)  $v_{ao} = V_{dc}/2$  and  $i_a > 0$ , c)  $v_{ao} = -V_{dc}/2$  and  $i_a > 0$  and d)  $v_{ao} = -V_{dc}/2$  and  $i_a < 0$ .

Other alternative single-phase topology is the H-bridge VSI (also known as full-bridge). Basically it is composed by two half-bridge inverter legs in parallel connection to provide two output nodes a and b, to connect the load between them (as Fig. 2.5 shows). For this reason, the midpoint in the dc link is no longer necessary, hence just one capacitor is required.

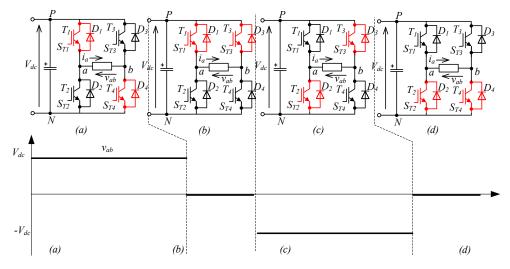

Since this inverter is controlled with two complementary binary signals ( $S_{TI}$  and  $S_{T2}$ ,  $S_{T3}$  and  $S_{T4}$ ), it generates  $2^2 = 4$  different switching states, which are illustrated in Fig. 2.6, and an arbitrary switching pattern is produced. Possible output voltage values and switching states are summarized in Table 2.2.

A general expression for the output voltage is:

$$v_{ab} = (S_{TI} - S_{T3})V_{dc}, \quad S_{Ti} \in \{0,1\}.$$

(2.1)

Note that there are two switching combinations that generate both a zero voltage level. This feature is known as redundancy, which can be used for other purpose since it does not affect the voltage applied to the load.

Likewise in the previous topology, each power switch is blocking the total  $V_{dc}$  when not conducting. Therefore, like in the previous case, this topology is also limited to low voltage range. Nevertheless, the H-bridge can be used as a basic module for larger multilevel converters, with more voltage levels, suitable for medium-voltage applications [14].

Fig. 2.5. H-bridge inverter power circuit (IGBT based).

Fig. 2.6. H-bridge switching states. a)  $v_{ab} = V_{dc}$ , b)  $v_{ab} = 0$ , c)  $v_{ab} = -V_{dc}$  and d)  $v_{ab} = 0$ .

Table 2.2. H-bridge switching states.

| Switching state | Gate signal $(S_{TI})$ | Gate sig-nal $(S_{T3})$ | Output<br>voltage |

|-----------------|------------------------|-------------------------|-------------------|

| 1               | 1                      | 0                       | $V_{dc}$          |

| 2               | 1                      | 1                       | 0                 |

| 3               | 0                      | 1                       | $-V_{dc}$         |

| 4               | 0                      | 0                       | 0                 |

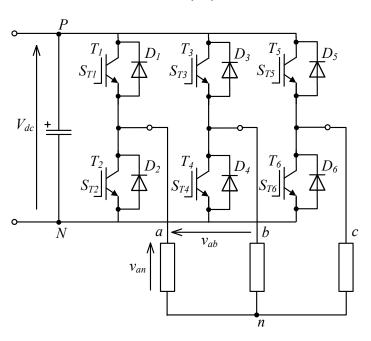

# 2.2.2 Three phase

The three-phase VSI is built with three paralleled inverter legs, as the same as shown before for the half- and-H bridge, as depicted in Fig. 2.7. It has a similar operation. Each inverter branch has its own binary and complementary signal for identical reasons. The inverter phase output voltages can be obtained by

$$V_{xN} = S_{Tx} V_{dc}, \quad S_{Ti} \in \{0,1\}, \quad x = a, b, c.$$

(2.2)

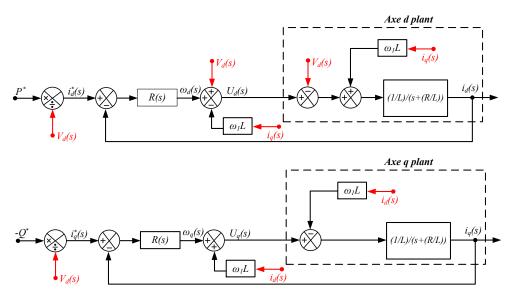

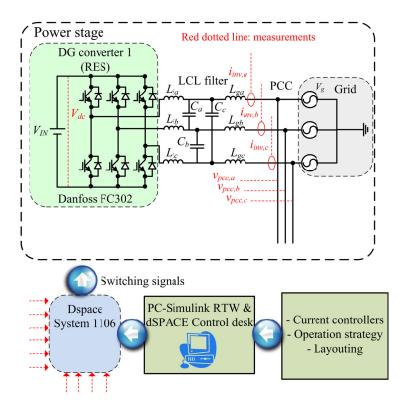

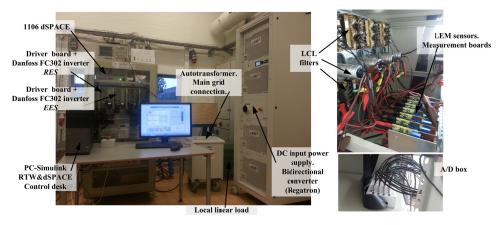

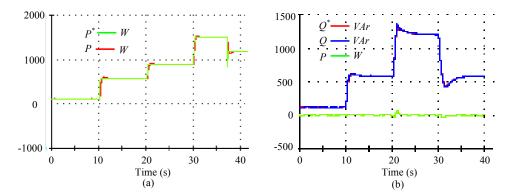

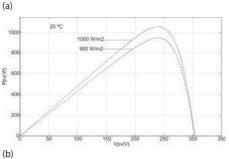

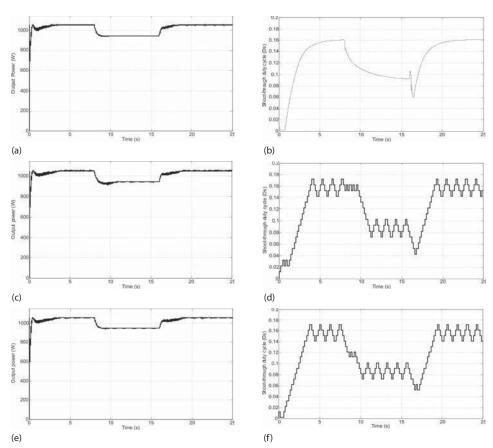

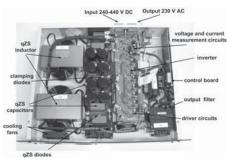

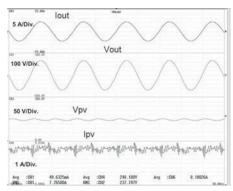

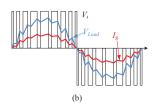

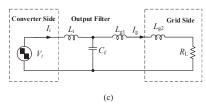

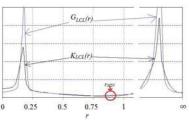

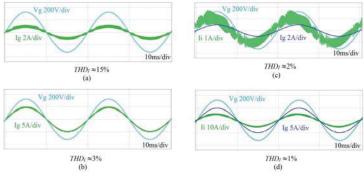

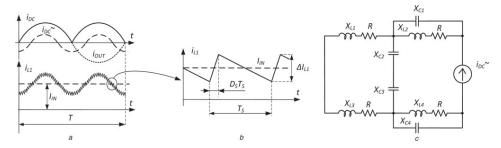

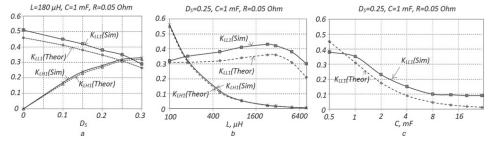

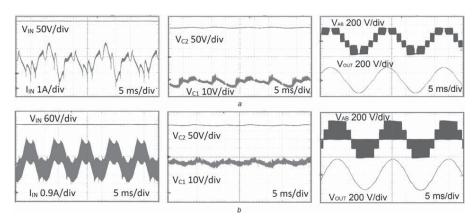

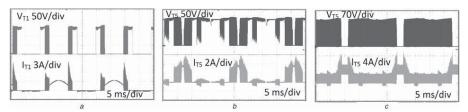

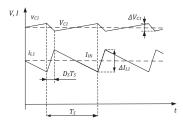

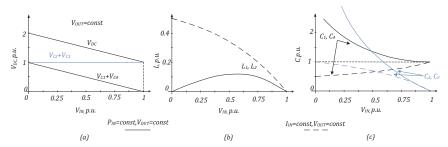

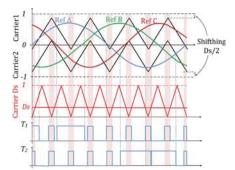

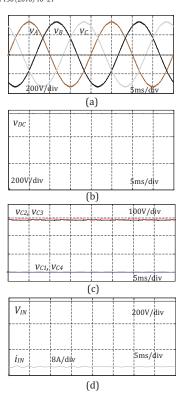

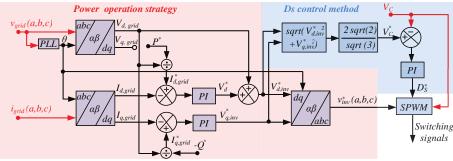

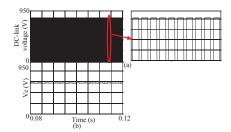

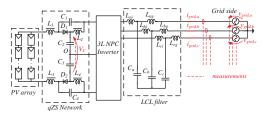

Fig. 2.7. Full-bridge three-phase VSI topology (with Y-connected load).